# Synthesis of Combinational Logic

Lab 1 is due Thursday 9/22 Quiz 1 is Friday 9/23 (in section)

LO4 - Logic Synthesis 1

# Functional Specifications

There are many ways of specifying the function of a combinational device, for example:

Concise alternatives:

truth tables are a concise description of the combinational system's function.

Boolean expressions form an algebra in whose operations are AND (multiplication), OR (addition), and inversion (overbar).

Any combinational (Boolean) function can be specified as a truth table or an equivalent sum-of-products Boolean expression!

6.004 - Fall 2011

LO4 - Logic Synthesis 2

Truth Table

$Y = \overline{CBA} + \overline{CBA} + \overline{CBA} + \overline{CBA} + \overline{CBA}$

6.004 - Fall 2011

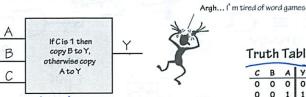

Here's a Design Approach hay & by A

Truth Table

1) Write out our functional spec as a truth table

0

2) Write down a Boolean expression with terms covering each '1' in the

Y=CBA+CBA+CBA+CBA/ust look

3) Wire up the gates, call it a day, and declare success!

-it's systematic! -it's easy

This approach will always give us Boolean expressions in a particular form: SUM-OF-PRODUCTS

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 3

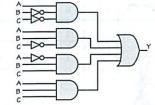

Straightforward Synthesis

I toolproof way to implement

We can implement

SUM-OF-PRODUCTS

with just three levels of

logic.

INVERTERS/AND/OR

Propagation delay --

No more than 3 gate delays

(assuming gates with an arbitrary number of inputs)

wolft case for any boblean expression

6.004 - Fall 2011

LO4 - Logic Synthesis 4

# Basic Gate Repertoire

Are we sure we have all the gates we need? Just how many two-input gates are there?

there y chosen

| AN | D | 01 | R | NA | ND | NO | R |

|----|---|----|---|----|----|----|---|

| AB | У | AB | У | AB | У  | AB | У |

| 00 | 0 | 00 | 0 | 00 | 1  | 00 | 1 |

| 01 | 0 | 01 | 1 | 01 | 1  | 01 | 0 |

| 10 | 0 | 10 | 1 | 10 | 1  | 10 | 0 |

| 11 | 1 | 11 | 1 | 11 | 0  | 11 | 0 |

Hmmmm... all of these have 2-inputs (no surprise)

... each with 4 combinations, giving 22 output cases

$2^{2^{2}} = 2^{4} = 16$  4 from

How many ways are there of assigning 4 outputs?

04 - Logic Synthesis 5

6.004 - Fall 2011

Ih two value functions

## Logic Geek Party Games

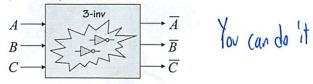

You have plenty of ANDs and ORs, but only 2 inverters. Can you invert more than 2 independent inputs?

CHALLENGE: Come up with a combinational circuit using ANDs, ORs, and at most 2 inverters that inverts A, B, and C!

Such a circuit exists. What does that mean?

- If we can invert 3 signals using 2 inverters, can we use 2 of the pseudoinverters to invert 3 more signals?

- Do we need only 2 inverters to make ANY combinational circuit?

Hint: there's a subtle difference between our 3-inv device and three combinational inverters!

Is our 3-inv device LENIENT?

3.004 - Fall 2011

On output feeds but he as an inpi

## There are only so many gates

There are only 16 possible 2-input gates

... some we know already, others are just silly

| I      |   |   |   |   |   |   |   |   |   |   |     |    |     |    |   |   |

|--------|---|---|---|---|---|---|---|---|---|---|-----|----|-----|----|---|---|

| N<br>P |   |   |   |   |   |   |   |   |   |   |     |    |     |    |   |   |

| P      | Z |   |   |   |   |   |   |   |   | X | N   |    | N   |    | N |   |

| U      | E | A | A |   | В |   | X |   | N | N | 0   | A  | 0   | В  | A | 0 |

| T      | R | N | > |   | > |   | 0 | 0 | 0 | 0 | Т   | <= | T   | <= | N | N |

| AB     | 0 | D | В | A | A | В | R | R | R | R | 'B' | В  | 'A' | A  | D | Ε |

| 00     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1   | 1  | 1   | 1  | 1 | 1 |

| 01     | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0   | 0  | 1   | 1  | 1 | 1 |

| 10     | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1   | 1  | 0   | 0  | 1 | 1 |

| 11     | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0   | 1  | 0   | 1  | 0 | 1 |

N A O N N N D E

How many of

these gates can be

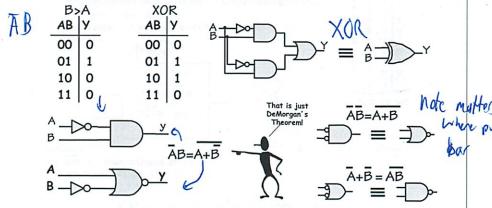

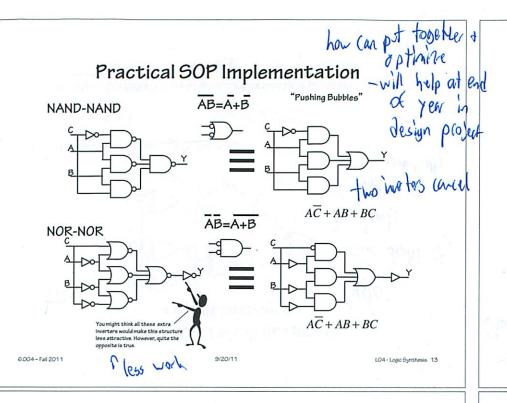

CMOS gates are inverting; we can always respond positively to positive transitions by cascaded gates. But suppose our logic yielded cheap positive functions, while inverters were expensive...

6004-FAIR2011 /thything where in 1-0 9/2011/10 0-31

LO4 - Logic Synthesis 6

(an not go 1->0 AND D->

So output transitions only apposet input

Fortunately, we can get by with a few basic gates...

AND, OR, and NOT are sufficient . . . (cf Boolean Expressions):

How many different gates do we really need?

petter to do w

LO4 - Logic Synthesis 8

VAMD gate

#### One will do!

NANDs and NORs are universal:

Ah!, but what if we want more than 2-inputs?

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 9

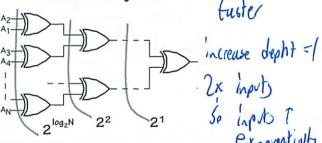

# Stupid Gate Tricks

Suppose we have some 2-input XOR gates:

And we want an N-input XOR:

Can cascale

output = 1iff number of 1s input is ODD ("ODD PARITY")

Can we compute N-input XOR faster?

$t_{pd} = O(N) - WORST CASE.$

6.004 - Fall 2011

LO4 - Logic Synthesis 10

You asking

#### I think that I shall never see

tree

a circuit lovely as...

N-input TREE has O( log N ) levels...

Signal propagation takes  $O(\frac{\log N}{\log N})$  gate delays.

Question: Can EVERY N-Input Boolean function be implemented as a tree of 2-input gates?

6.004 - Fall 2011

LO4 - Logic Synthesis 11

Other Strategies Are Trees Always Best?

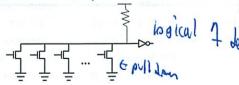

Alternate Plan: Large Fan-in gates Wa

N pulldowns with complementary pullups

• Output HIGH if any input is HIGH = "OR"

Propagation delay: O(N) since each additional MOSFET adds C

Don't be mislead by the "big O" stuff... the constants in this case can be much smaller... so for small N this plan might be the best.

9/20/11

LO4 - Logic Synthesis 12

Know roles

Can we implement the same function with fewer gates? Before trying we'll add a few more tricks in our bag.

#### **BOOLEAN ALGEBRA:**

OR rules: a+1=1, a+0=a, a+a=a

AND rules: a1 = a, a0 = 0, aa = a

Commutative: a+b=b+a, ab=ba

Associative:

(a+b)+c=a+(b+c), (ab)c=a(bc)a(b+c) = ab + ac, a + bc = (a+b)(a+c)

Complements:

$a+\overline{a}=1$ ,  $a\overline{a}=0$

Absorption:

Distributive:

a+ab=a,  $a+\overline{a}b=a+b$

a(a+b)=a,  $a(\overline{a}+b)=ab$

Reduction:

$ab+\overline{a}b=b$ ,  $(a+b)(\overline{a}+b)=b$

DeMorgan's Law:  $\overline{a} + \overline{b} = \overline{ab}$ ,  $\overline{ab} = \overline{a+b}$

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 14

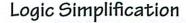

# **Boolean Minimization:**

An Algebraic Approach

Lets (again!) simplify

$Y = \overline{CB}A + CB\overline{A} + CBA + \overline{C}BA$

Using the identity

6.004 - Fall 2011

$\alpha A + \alpha \overline{A} = \alpha$  to a while only

For any expression C and variable A

$Y = \overline{CBA} + CB\overline{A} + CBA + \overline{CBA}$

$Y = \overline{CBA} + CB + \overline{CBA}$

$Y = \overline{C}A + CB$

Hey, I could write A program to do

Can combin

Can't he come up

with a new example???

#### Truth Tables with "Don't Cares"

One way to reveal the opportunities for a more compact implementation is to rewrite the truth table using "don't cares" (--) to indicate when the value of a particular input is irrelevant in determining the value of the

|   |   |   |           |   |   |   |   | 1,00004                              |

|---|---|---|-----------|---|---|---|---|--------------------------------------|

| С | B | A | Y         |   |   |   | 1 | 1 Pour                               |

| 0 |   | 0 | 0         | С | В | A | Y | -can be 0                            |

| 0 | 0 | 1 | 1         | 0 |   | 0 | 0 |                                      |

| 0 | 1 | 0 | 0) 1      | 0 |   | 1 | 1 | $\rightarrow \overline{C}A$ or other |

| 0 | 1 | 1 | 1 1/00001 | 1 | 0 |   | 0 |                                      |

| 1 | 0 | 0 | o repeat  | 1 | 1 |   | 1 | CD.                                  |

| 1 | 0 | 1 | 0         |   |   |   | ' | $\rightarrow CB$                     |

| 1 | 1 | 0 | 1         |   |   | 0 | 0 |                                      |

| 1 | 1 | 1 | 1         |   | 1 | 1 | 1 | $\longrightarrow BA$                 |

|   |   |   |           |   |   |   | • |                                      |

6.004 - Fall 2011

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 17

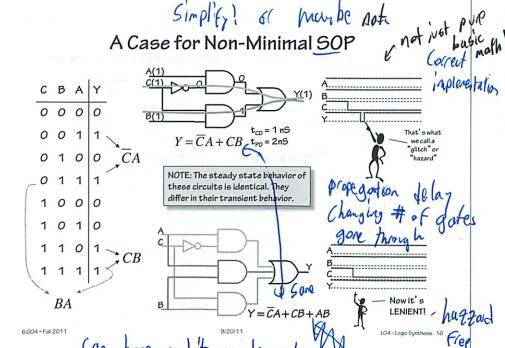

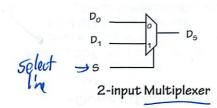

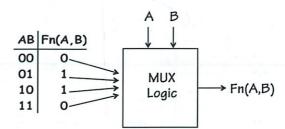

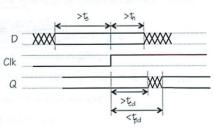

# We've been designing a "mux"

What it hadware fixed?

MUXes can be generalized to 2k data inputs and k select inputs ...

... and implemented as a

tree of smaller MUXes:

LO4 - Logic Synthesis 18

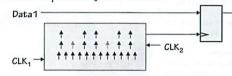

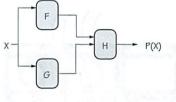

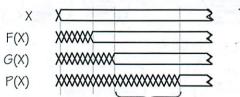

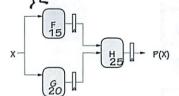

# Systematic Implementations of Combinational Logic

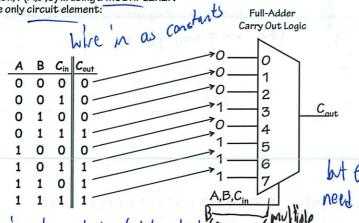

Consider implementation of some arbitrary Boolean function, F(A,B,C) ... using a MULTIPLEXER as the only circuit element:

# General Table Lookup Synthesis

Generalizina:

In theory, we can build any 1-output combinational logic block with multiplexers.

For an N-input function we need a 2 input mux.

Is this practical for BIG truth tables? How about 10-input function? 20-input?

6.004 - Fall 2011

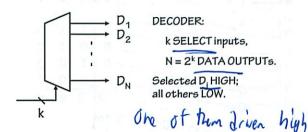

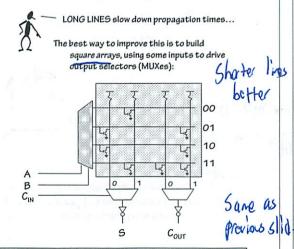

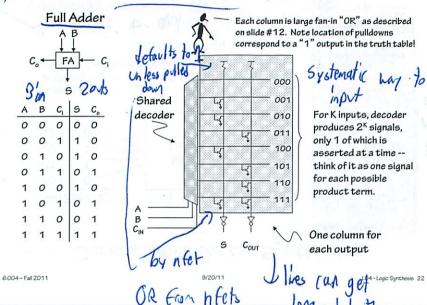

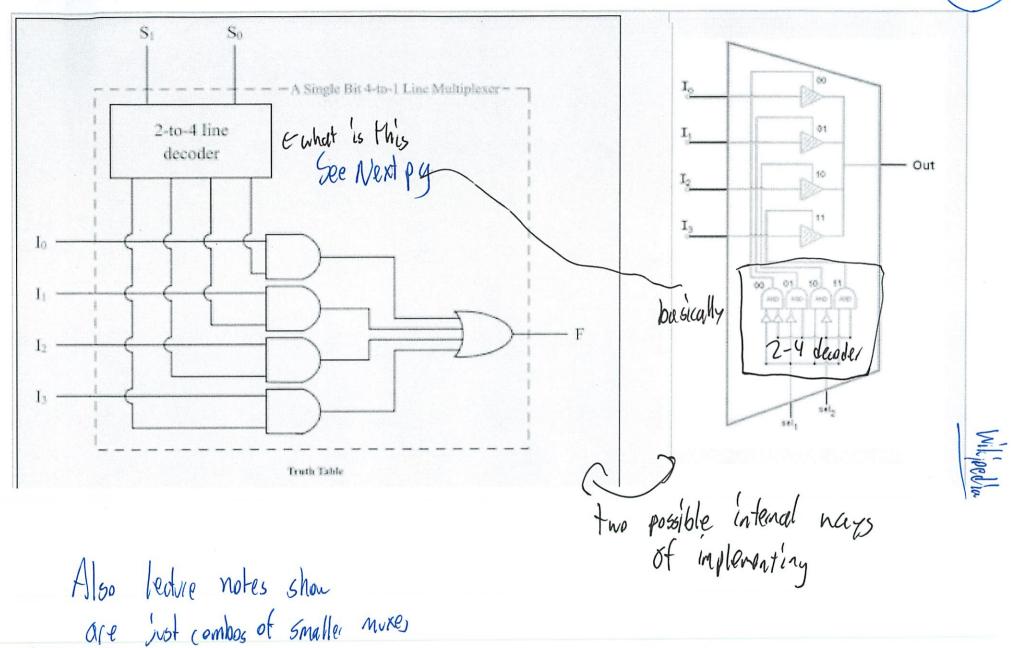

# A New Combinational Device - but looks lik it

NOW, we are well on our way to building a general purpose table-lookup device.

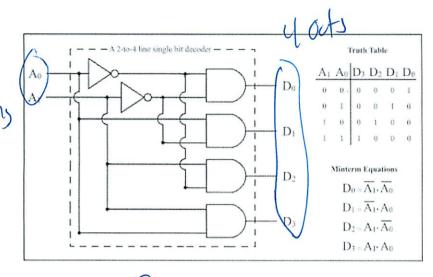

We can build a 2-dimensional ARRAY of decoders and selectors as follows ...

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 21

# is a synonym LOW means

Have I mentioned that HIGH

# Read-only memories (ROMs)

2D Addressing: Standard for ROMs, RAMs, logic arrays...

6.004 - Fall 2011

Secret same Within ( ROM

#### Read-only memories (ROMs)

Caparatane

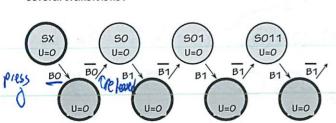

# Logic According to ROMs

ROMs ignore the structure of combinational functions ...

- · Size, layout, and design are independent of function

- · Any Truth table can be "programmed" by minor reconfiguration:

- Metal layer (masked ROMs)

- Fuses (Field-programmable PROMs)

- Charge on floating gates (EPROMs) ... etc.

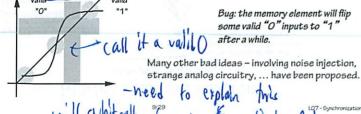

generate "glitchy" outputs. WHY?

ROMs tend to

Model: LOOK UP value of function in truth table...

₱ Inputs: "ADDRESS" of a T.T. entry

ROM SIZE = # TT entries...

... for an N-input boolean function, size  $\cong \frac{2^N \times \#outputs}{}$

# Summary

- · Sum of products

- Any function that can be specified by a truth table or, equivalently, in terms of AND/OR/NOT (Boolean expression)

- · "3-level" implementation of any logic function

- · Limitations on number of inputs (fan-in) increases depth

- · SOP implementation methods

- · NAND-NAND, NOR-NOR

- · Muxes used to build table-lookup implementations

- · Easy to change implemented function -- just change constants

- · ROMs

- · Decoder logic generates all possible product terms

- · Selector logic determines which p' terms are or' ed together

6.004 - Fall 2011

9/20/11

LO4 - Logic Synthesis 25

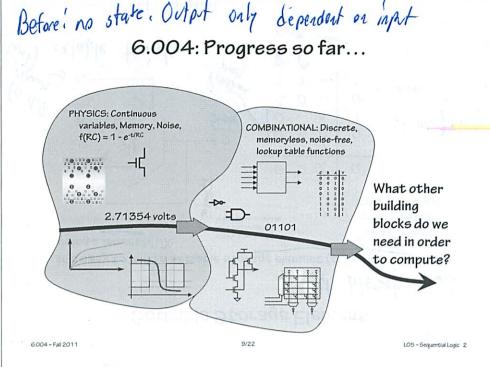

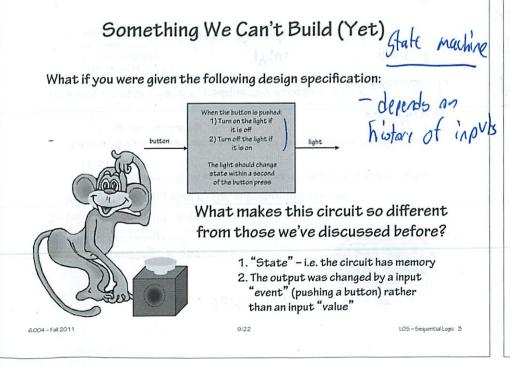

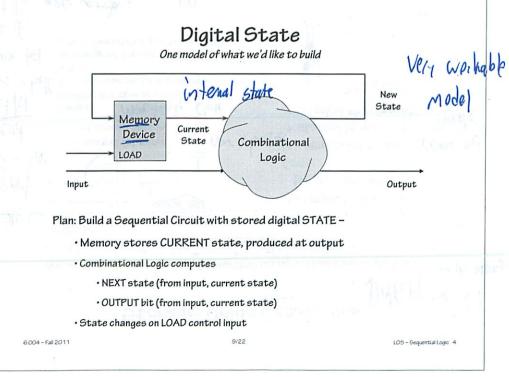

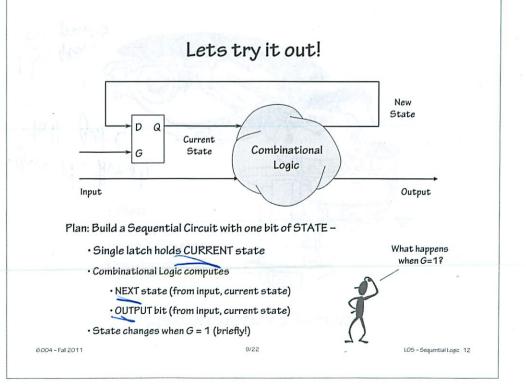

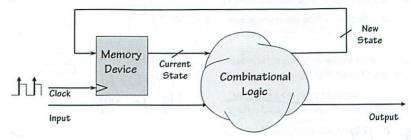

Needed: Storage

Combinational logic is stateless: valid outputs always reflect current inputs.

To build devices with state, we need components which store information (e.g., state) for subsequent access.

ROMs (and other combinational logic) store information "wired in" to their truth table

Read/Write memory elements are required to build devices capable of changing their contents. Use Physical

How can we store - and subsequently access -- a bit?

· Mechanics: holes in cards/tapes

· Optics: Film, CDs, DVDs, ...

· Magnetic materials

· Delay lines; moonbounce

· Stored charge

6.004 - Fall 2011

LO5 - Sequential Logic 5

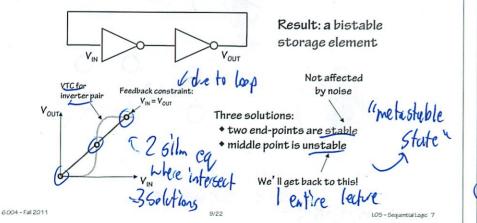

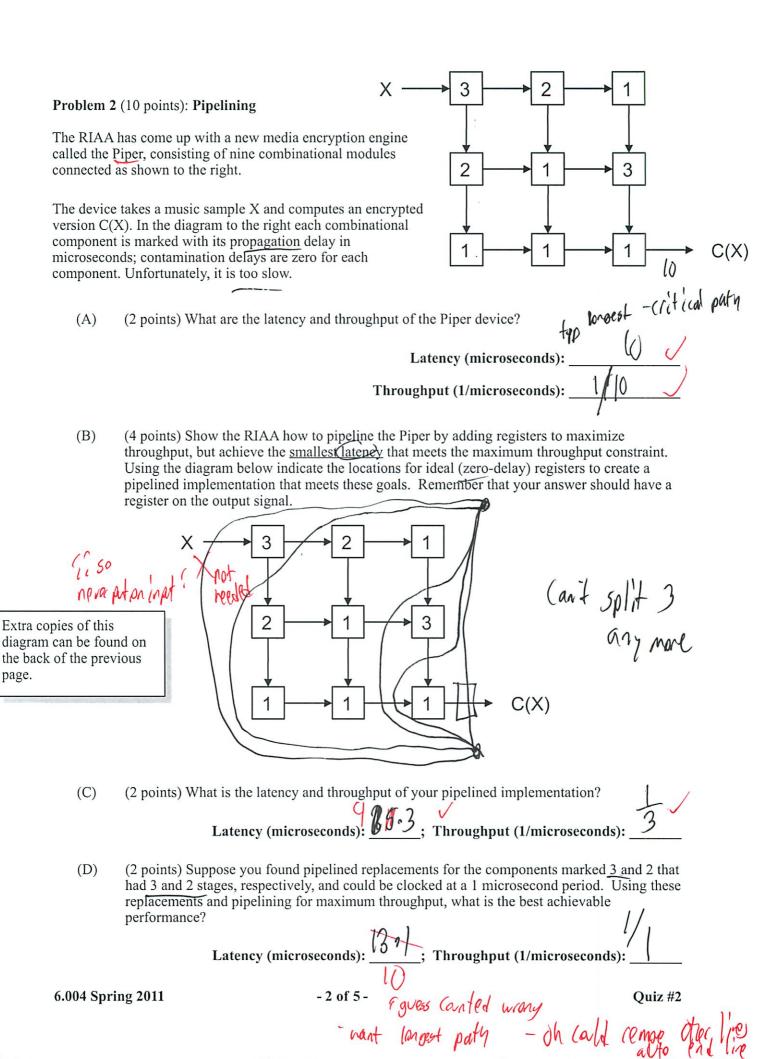

# Storage: Using Feedback bistule -7

IDEA: use positive feedback to maintain storage indefinitely. Stube Our logic gates are built to restore marginal signal levels, so noise shouldn't be a problem!

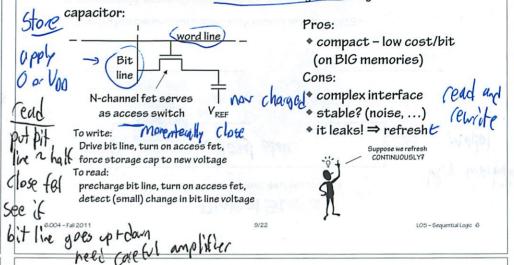

Storage: Using Capacitors

We've chosen to encode information using voltages and we know from 6.002 that we can "store" a voltage as charge on a

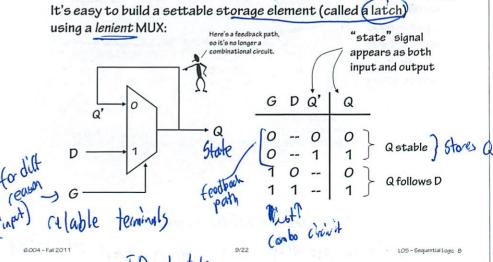

# Settable Storage Element

bistable behavior

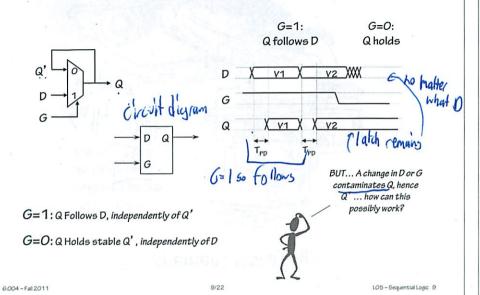

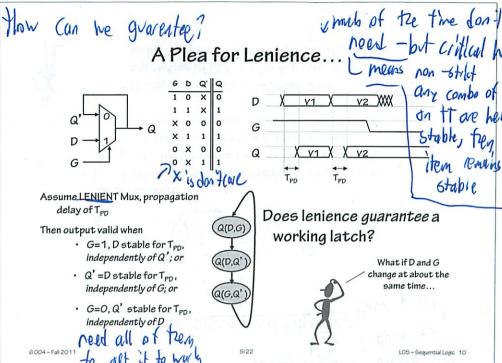

#### New Device: D Latch

Timing Diagram ... with a little discipline DStable V2-V2 To reliably latch V2: TPD · Apply V2 to D, holding G=1 TSETUP THOLD · After Tpp, V2 appears at Q=Q' thotal hat he  $\cdot$  After another  $T_{PD}$ , Q' & D both Dynamic Discipline for our latch: valid for Tpp; will hold Q=V2  $T_{SETUP} = 2T_{PD}$ : interval prior to G Independently of G stuble wall transition for which D must be · Set G=O, while Q' & D hold Q=D stable & valid ind. After another T<sub>PD</sub>, G=O and Q'  $T_{HOLD} = T_{PD}$ : interval following G are sufficient to hold Q=V2 transition for which D must be independently of D top stable & valid 6004-Fall 2011 Tdoes not depend 9/22 LO5 - Sequential Logic 11

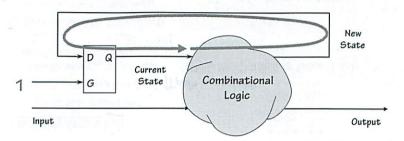

# Fransparent = Open

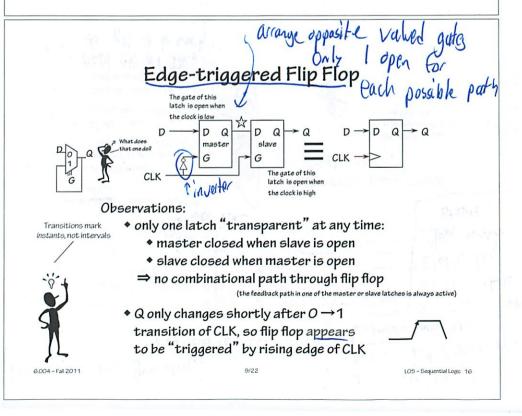

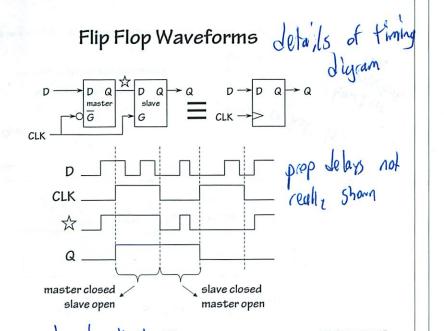

## Combinational Cycles

When G=1, latch is Transparent...

... provides a combinational path from D to Q.

Can't work without tricky timing constrants on G=1 pulse:

- Must fit within contamination delay of logic

- · Must accommodate latch setup, hold times

Want to signal an INSTANT, not an INTERVAL...

6.004 - Fall 2011

9/22

Looks like a stupid Approach to me...

LO5 - Sequential Logic 13

# Escapement Strategy

Um, about that hold time...

The master's contamination delay must meet the hold time of the slave  $Q = \frac{1}{G} \qquad Q$

Consider HOLD TIME requirement for slave:

- Negative  $(1 \rightarrow 0)$  clock transition  $\Rightarrow$  slave freezes data:

- SHOULD be no output glitch, since master held constant data; BUT

- master output contaminated by change in G input!

- HOLD TIME of slave not met, UNLESS we assume sufficient contamination delay in the path to its D input!

Accumulated  $t_{CD}$  thru inverter,  $G \rightarrow Q$  path of master must cover slave  $t_{HOLD}$  for this design to work!

6.004 - Fall 2011

need long cragh CO not 0 enot many of those

LO5 - Sequential Logic 18

external view

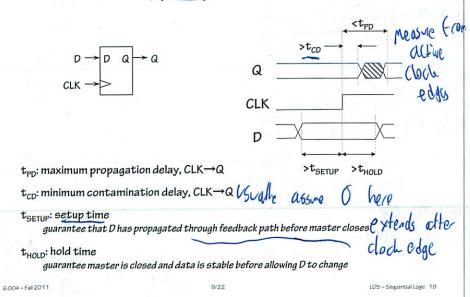

# Flip Flop Timing - I

6.004 - Fall 2011

Clear, Small celiable

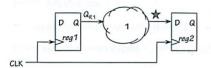

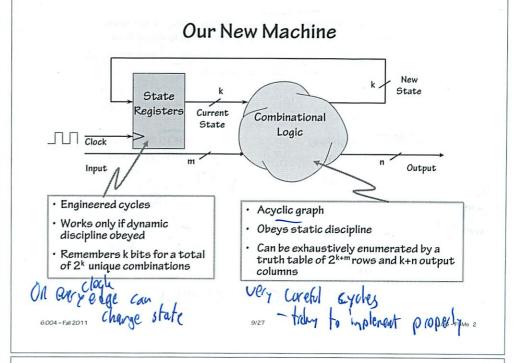

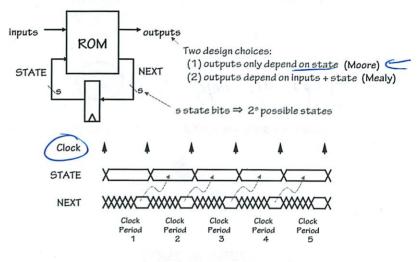

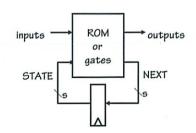

We'll use Flip Flops and Registers – groups of FFs sharing a clock input – in a highly constrained way to build digital systems:

# Does that symbol register? Single-clow No comb Single per among a combina Period go combina Change sinducing the symbol of the combina of the combination of the c

<u>Single-clock Synchronous Discipline</u>

- ·No combinational cycles Must go though register

- Single periodic clock signal shared among all clocked devices

- Only care about value of register data inputs just before rising edge of clock

- Period greater than every combinational delay + setup time

- Change saved state after noiseinducing logic transitions have stopped!

6.004 - Fall 2011

Clockvou

Etc. through each possible path

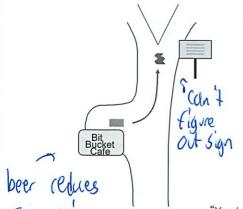

Flip Flop Timing - II

$$t_1 = t_{CD,reg1} + t_{CD,1} > t_{HOLD,reg2}$$

$$\mathbf{t_2} = \mathbf{t_{PD,reg1}} + \mathbf{t_{PD,1}} < \mathbf{t_{CLK}} - \mathbf{t_{SETUP,reg2}}$$

Questions for register-based designs

- how much time for useful work (i.e. for combinational logic delay)?

- \* does it help to quarantee a minimum to? How about designing registers so that

t<sub>CD.rea</sub> > t<sub>HOLD.rea</sub>?

what happens if CLK signal doesn't arrive at the two registers at exactly the same time (a phenomenon known as "clock skew"

6.004 - Fall 2011

Model: Discrete Time w/ clock perints

more

Active Clock Edges punctuate time ---

- · Discrete Clock periods

- · Discrete State Variables

- · Discrete specifications (simple rules eg tables relating outputs to inputs, state variables)

- · ABSTRACTION: Finite State Machines (next lecture!)

Can simplify a lot 6.004 - Fall 2011

LO5 - Sequential Logic 22

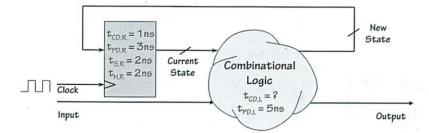

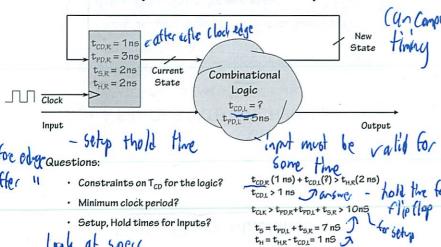

# Sequential Circuit Timing

#### Questions:

- · Constraints on Tcp for the logic?

- · Minimum clock period?

- · Setup, Hold times for Inputs?

>1 ns to for hold the

$T_H = T_{HR} - T_{CDL}$

IVN

This is a simple Finite State Machine ... more next lecture!!

Summary

"Sequential" Circuits (with memory):

#### Basic memory elements:

- Feedback, detailed analysis => basic level-sensitive devices (eg, latch)

- 2 Latches => Flop

- Dynamic Discipline: constraints on input timing

#### Synchronous 1-clock logic:

- Simple rules for sequential

- Yields clocked circuit with Ts, TH constraints on input timing

Next Lecture Topic!

6.004 - Fall 2011

9/22

LO5 - Sequential Logic 24

# Two's complement

From Wikipedia, the free encyclopedia

Read 8/25

The **two's complement** of a binary number is defined as the value obtained by subtracting the number from a large power of two (specifically, from  $2^N$  for an N-bit two's complement). The two's complement of the number then behaves like the negative of the original number in most arithmetic, and it can coexist with positive numbers in a natural way.

Two's Complement is referred to as Binary Number Representation (or BNR) in protocols used in Aviation (ARINC\_429).

A two's-complement system, or two's-complement arithmetic, is a system in which negative numbers are represented by the two's complement of the absolute value; [1] this system is the most common method of representing signed integers on computers. [2] In such a system, a number is negated (converted from positive to negative or vice versa) by computing its two's complement. An N-bit two's-complement numeral system can represent every integer in the range  $-2^{N-1}$  to  $2^{N-1}$ -1.

The two's-complement system has the advantage of not requiring that the addition and subtraction circuitry examine the signs of the operands to determine whether to add or subtract. This property makes the system both simpler to implement and capable of easily handling higher precision arithmetic. Also, zero has only a single representation, obviating the subtleties associated with negative zero, which exists in ones'-complement systems.

The method of complements can also be applied in base-10 arithmetic, using ten's complements by analogy with two's complements.

#### Contents

- 1 Explanation

- 1.1 Two's-complement numbers

- 1.2 Making the Two's Complement of a number

- 1.3 Alternative conversion process

- 1.4 Sign extension

- 1.5 The most negative number

- 1.6 Why it works

- 1.7 Calculating two's complement

- 2 Arithmetic operations

- 2.1 Addition

- 2.2 Subtraction

- 2.3 Multiplication

- 3 Two's complement and universal algebra

- 4 Potential ambiguities in usage

- 5 See also

- 6 External links

- 7 References

| significa | nnt<br>bit | 1 |   |   |   |   |   |   |     |      |   |

|-----------|------------|---|---|---|---|---|---|---|-----|------|---|

|           | 0          | 1 | 1 | 1 | 1 | 1 | 1 | 1 | =   | 127  |   |

|           | 0          | 1 | 1 | 1 | 1 | 1 | 1 | 0 | =   | 126  |   |

|           | 0          | 0 | 0 | 0 | 0 | 0 | 1 | 0 | =   | 26   | 6 |

|           | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 1 | =   | 1    | _ |

|           | Q          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | =   | 0    |   |

|           | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 1 | =   | -1   |   |

|           | 1          | 1 | 1 | 1 | 1 | 1 | 1 | 0 | =   | -2   |   |

|           | 1          | 0 | 0 | 0 | 0 | 0 | 0 | 1 | = - | -127 |   |

|           | 1          | 0 | 0 | 0 | 0 | 0 | 0 | 0 | =-  | -128 |   |

## Explanation

#### Two's-complement numbers

Two's complement numbers is a way to encode negative numbers into ordinary binary, such that addition still works. Adding -1 + 1 should equal 0, but ordinary addition gives the result of 2 or -2 unless the operation takes special notice of the sign bit and performs a subtraction instead. Two's complement results in the correct sum without this extra step.

A two's-complement number system encodes positive and negative numbers in a binary number representation. The bits have a binary radix point and the bits are weighted according to the position of the bit within the array. A convenient notation is the big-endian ordering. In this notation, the bit to the left of the binary point has a bit index of 0 and a weight of  $2^0$ . The bit indices increase, by one, to the left of the binary point, and decrease, by one, to the right of the binary point. The weight of each bit is  $2^i$ , except for the left-most bit, whose weight is  $-2^i$ . With this bit

-2,5652654 53555150

numbering, a two's complement number with m integer bits and n fractional bits is represented by the array of bits

$$v = a_{m-1}, a_{m-2}, \dots, a_1, a_0.a_{-1}, a_{-2}, \dots a_{-n}.$$

Tale we doing tractional bits

The value of this number is given by the following formula.

$$-a_{m-1} \times 2^{m-1} + \sum_{i=-n}^{m-2} a_i \times 2^i$$

The left-most bit, also called the most-significant bit (MSB), determines the sign of the number, but, unlike the sign-and-magnitude representation, also has a weight,  $-2^{m-1}$ , as shown in the formula above. Because of this weight, it is misleading to call this bit the "sign bit".

The two's complement encoding shown above can represent the following range of numbers

Zero representation is

rhat this?

$0:0,0,\ldots,0$  The maximum positive number

$$2^{m-1} - 2^{-n} : 0, 1, 1, 1, \dots, 1, 1$$

The minimum, non-zero, positive number (smallest absolute value) is

$$2^{-n}:0,0,0,\ldots,0,0,1$$

The minimum negative number is

$$-2^{m-1}:1,0,0,0,\ldots,0,0$$

The maximum negative number (smallest absolute value) is

$$-2^{-n}:1,1,1,\ldots,1,1$$

#### Making the Two's Complement of a number

Positive numbers are represented in two's complement as binary numbers whose most significant bit is zero. Negative numbers are represented with the most-significant bit being one, making use of the left-most bit's negative weight. All radix complement number systems use a fixed-width encoding. Every number encoded in such a system has a fixed width so the most-significant digit can be examined.

Algorithmically, to create a two's complement binary value:

- 1. express the binary value for the positive number

- 2. if the original value was negative,

- 2a. complement the value

- 2b. add one

- 3a. if the value is positive, add leading zeros to achieve the proper number of bits

- 3b. if the value is negative, add leading ones to achieve the proper number of bits

- (3. replicate the MSB to achieve the proper number of bits)

In general, for a radix r's complement encoding, with r the base (radix) of the number system, an integer part of m digits and fractional part of n digits, then the r's complement of a number  $0 \le N < r^{m-1} - r^{-n}$  is determined by the formula:

$$N^{**} = (r^m - N) \mod (r^m)$$

The (r-1)'s complement of a number is determined by the formula:

We can also find the r's complement of a number N by adding  $r^{-n}$  to the (r-1)'s complement of the number i.e.,

$N^{**} = N^* + r^{-n}$

#### Alternative conversion process

A shortcut to manually convert a binary number into its two's complement is to start at the least significant bit (LSB), and copy all the zeros (working from LSB toward the most significant bit) until the first 1 is reached; then copy that 1, and flip all the remaining bits. This shortcut allows a person to convert a number to its two's complement without first forming its ones' complement. For example: the two's complement of "0011 1100" is "1100 0100", where the underlined digits were unchanged by the copying operation (while the rest of the digits were flipped).

-----

In computer circuitry, this method is no faster than the "complement and add one" method; both methods require working sequentially from right to left, propagating logic changes. The method of complementing and adding one can be sped up by a standard carry look-ahead adder circuit; the alternative method can be sped up by a similar logic transformation.

#### Sign extension

When turning a two's-complement number with a certain number of bits into one with more bits (e.g., when copying from a 1 byte variable to a two byte variable), the most-significant bit must be repeated in all the extra bits and lower bits.

| Decimal    | 4-bit notation | 8-bit notation |

|------------|----------------|----------------|

| 5          | 0101           | 0000 0101      |

| <b>-</b> 5 | 1011           | 1111 1011      |

Some processors have instructions to do this in a single instruction. On other processors a conditional must be used followed with code to set the relevant bits or bytes.

sign-bit repetition in 4 and 8-bit integers

Similarly, when a two's-complement number is shifted to the right, the most-significant bit, which contains magnitude and the sign information, must be maintained. However when shifted to the left, a 0 is shifted in. These rules preserve the common semantics that left shifts multiply the number by two and right shifts divide the number by two.

Both shifting and doubling the precision are important for some multiplication algorithms. Note that unlike addition and subtraction, precision extension and right shifting are done differently for signed vs unsigned numbers.

#### The most negative number

With only one exception, when we start with any number in two's-complement representation, if we flip all the bits and add 1, we get the two's-complement representation of the negative of that number. Negative 12 becomes positive 12, positive 5 becomes negative 5, zero becomes zero, etc.

The two's complement of the minimum number in the range will not have the desired effect of negating the number. For example, the two's complement of -128 in an 8-bit system results in the same binary number. This is because a positive value of 128 cannot be represented with an 8-bit signed binary numeral. Note that this is detected as an overflow condition since there was a carry into but not out of the most-significant bit. This can lead to unexpected bugs in that a naive implementation of absolute value could return a negative number.

| -128        | 1000 0000 |

|-------------|-----------|

| invert bits | 0111 1111 |

| add one     | 1000 0000 |

The two's complement of -128 results in the same 8-bit binary number.

The most negative number in two's complement is sometimes called "the weird number," because it is the only exception. [3][4]

Although the number is an exception, it is a valid number in regular two's complement systems. All arithmetic operations work with it both as an operand and (unless there was an overflow) a result.

#### Why it works

Given a set of all possible n-bit values, we can assign the lower (by binary value) half to be the integers from 0 to  $(2^{n-1}-1)$  inclusive and the upper half to be  $-2^{n-1}$  to -1 inclusive. The upper half can be used to represent negative integers from  $-2^{n-1}$  to -1 because, under addition modulo  $2^n$  they behave the same way as those negative integers. That is to say that because  $i + j \mod 2^n = i + (j - 2^n) \mod 2^n$  any value in the set  $\{j + k2^n \mid k \text{ is an integer}\}$  can be used in place of j.

For example, with eight bits, the unsigned bytes are 0 to 255. Subtracting 256 from the top half (128 to 255) yields the signed bytes -128 to 127.

The relationship to two's complement is realised by noting that 256 = 255 + 1, and (255 - x) is the ones' complement of x.

#### Example

-95 modulo 256 is equivalent to 161 since

-95 + 256

= -95 + 255 + 1

= 255 - 95 + 1

= 160 + 1

= 161

| -  |       |      |        |             | - |      |  |

|----|-------|------|--------|-------------|---|------|--|

| :  | 1111  | 1111 |        |             |   | 255  |  |

| -  | 0101  | 1111 |        |             | - | 95   |  |

| ;= | ===== | ==== |        |             | = | ==== |  |

| :  | 1010  | 0000 | (ones' | complement) |   | 160  |  |

| 1+ |       | 1    |        |             | + | 1    |  |

| •          |       |      |        |             |       |

|------------|-------|------|--------|-------------|-------|

| <u>'</u> = | ===== | ==== |        |             | ===== |

| i          | 1010  | 0001 | (two's | complement) | 161   |

| Decimal | Two's complement |

|---------|------------------|

| 127     | 0111 1111        |

| 64      | 0100 0000        |

| 1       | 0000 0001        |

| 0       | 0000 0000        |

| -1      | 1111 1111        |

| -64     | 1100 0000        |

| -127    | 1000 0001        |

| -128    | 1000 0000        |

Some special numbers to note

Fundamentally, the system represents negative integers by counting backward and wrapping around. The boundary between positive and negative numbers is arbitrary, but the defacto rule is that all negative numbers have a left-most bit (most significant bit) of one. Therefore, the most positive 4-bit number is 0111 (7) and the most negative is 1000 (-8). Because of the use of the left-most bit as the sign bit, the absolute value of the most negative number (|-8|=8) is too large to represent. For example, an 8-bit number can only represent every integer from -128 to 127 ( $2^{(8-1)}=128$ ) inclusive. Negating a two's complement number is simple: Invert all the bits and add one to the result. For example, negating 1111, we get 0000+1=1. Therefore, 1111 must represent -1.

The system is useful in simplifying the implementation of arithmetic on computer hardware. Adding 0011 (3) to 1111 (-1) at first seems to give the incorrect answer of 10010. However, the hardware can simply ignore the left-most bit to give the correct answer of 0010 (2). Overflow checks still must exist to catch operations such as summing 0100 and 0100.

The system therefore allows addition of negative operands without a subtraction circuit and a circuit that detects the sign of a number. Moreover, that addition circuit can also perform subtraction by taking the two's complement of a number (see below), which only requires an additional cycle or its own adder circuit. Lastly, the two's complement system allows a subtraction circuit to return 1001, equivalent to -0001, for 0001-0010 rather than 1111. To perform the former, the circuit merely pretends an extra left-most bit of 1 exists. To perform the latter, there must be a sign check, a possible rearrangement of the number, and finally a subtraction.

| Two's complement | Decimal     | So bayla<br>one means |

|------------------|-------------|-----------------------|

| 0111             | 7           | ب مسرر                |

| 0110             | 6           | One megne             |

| 0101             | 5           | allai                 |

| 0100             | 4           | al la                 |

| 0011             | 3           | 1-                    |

| 0010             | 2           | 60 7                  |

| 0001             | 1 2         | 2 1 28                |

| 0000             |             | 4214 28               |

| 1111             | -1 <b>(</b> | 1+2+1                 |

| 1110             | -2          |                       |

| 1101             | -3          | Oh easy               |

| 1100             | -4          |                       |

| 1011             | -5          | first is -            |

| 1010             | -6          | 1 +                   |

| 1001             | -7          | Oh 6                  |

| 1000             | -8          | 1, 100                |

| Two's complemen  | t using a   | it chot 1             |

# Two's complement using a 4-bit integer

In two's complement notation, a positive number is represented by its ordinary binary representation, using enough bits that the high bit (the sign bit) is 0. The two's complement operation is the negation operation, so negative numbers are represented by the two's complement of the representation of the absolute value.

In finding the two's complement of a binary number, the bits are inverted, or "flipped", by using the bitwise NOT  $-\frac{23}{8} + \frac{20}{100}$  operation; the value of 1 is then added to the resulting value. Bit overflow is ignored, which is the normal case with the zero value.

For example, beginning with the signed 8-bit binary representation of the decimal value 5, using subscripts to indicate the base of a representation needed to interpret its value:

$$00000101_2 = 5_{10}$$

Calculating two's complement

Now how do you add 1

09/23/2011 11:44 AM

I guess we will bean about

The most significant bit is 0, so the pattern represents a non-negative (positive) value.

To convert to -5 in two's-complement notation, the bits are inverted; 0 becomes 1, and 1 becomes 0:

11111010

At this point, the numeral is the ones' complement of the decimal value 5. To obtain the two's complement, 1 is added to the result, giving:

$$11111011_2 = -5_{10}$$

The result is a signed binary number representing the decimal value -5 in two's-complement form. The most significant bit is 1, so the value represented is negative.

The two's complement of a negative number is the corresponding positive value. For example, inverting the bits of -5 (above) gives:

00000100

And adding one gives the final value:

$$00000101_2 = 5_{10}$$

The value of a two's-complement binary number can be calculated by adding up the power-of-two weights of the "one" bits, but with a negative weight for the most significant (sign) bit; for example:

$$111111011_2 = -128 + 64 + 32 + 16 + 8 + 0 + 2 + 1 = (-2^7 + 2^6 + ...) = -5$$

Note that the two's complement of zero is zero: inverting gives all ones, and adding one changes the ones back to zeros (the overflow is ignored). Also the two's complement of the most negative number representable (e.g. a one as the most-significant bit and all other bits zero) is itself. Hence, there appears to be an 'extra' negative number.

A more formal definition of a two's-complement negative number (denoted by  $N^*$  in this example) is derived from the equation  $N^* = 2^n - N$ , where N is the corresponding positive number and n is the number of bits in the representation.

For example, to find the 4 bit representation of -5:

$$N = 5_{10}$$

therefore  $N = 0101_2$

$n = 4$

Hence:

$$N * = 2^n - N = 2^4 - 5_{10} = 10000_2 - 0101_2 = 1011_2$$

Year how do it in reverse ? take 7 to 1111

The calculation can be done entirely in base 10, converting to base 2 at the end:

$$N * = 2^n - N = 2^4 - 5 = 11_{10} = 1011_2$$

## Arithmetic operations

#### Addition

Adding two's-complement numbers requires no special processing if the operands have opposite signs: the sign of the result is determined automatically. For example, adding 15 and -5:

11111 111 (carry) 0000 1111 (15) + 1111 1011 (-5) 0000 1010 (10)

So AND each bit?

but the carry

This process depends upon restricting to 8 bits of precision; a carry to the (nonexistent) 9th most significant bit is ignored, resulting in the arithmetically correct result of  $10_{10}$ .

The last two bits of the carry row (reading right-to-left) contain vital information: whether the calculation resulted in an arithmetic overflow, a number too large for the binary system to represent (in this case greater than 8 bits). An overflow condition exists when these last two bits are different from one another. As mentioned above, the sign of the number is encoded in the MSB of the result.

In other terms, if the left two carry bits (the ones on the far left of the top row in these examples) are both 1s or both 0s, the result is valid; if the left two carry bits are "1 0" or "0 1", a sign overflow has occurred. **Conveniently, an XOR operation on these two bits can quickly determine if an overflow condition exists.** As an example, consider the 4-bit addition of 7 and 3:

In this case, the far left two (MSB) carry bits are "01", which means there was a two's-complement addition overflow. That is,  $1010_2 = 10_{10}$  is outside the permitted range of -8 to 7.

In general, any two n-bit numbers may be added without overflow, by first sign-extending both of them to n+1 bits, and then adding as above. The n+1 bit result is large enough to represent any possible sum (e.g., 5 bits can represent values in the range -16 to 15) so overflow will never occur. It is then possible, if desired, to 'truncate' the result back to n bits while preserving the value if and only if the discarded bit is a proper sign extension of the retained result bits. This provides another method of detecting overflow—which is equivalent to the method of comparing the carry bits—but which may be easier to implement in some situations, because it does not require access to the internals of the addition.

#### Subtraction

Computers usually use the method of complements to implement subtraction. Using complements for subtraction is closely related to using complements for representing negative numbers, since the combination allows all signs of operands and results; direct subtraction works with two's-complement numbers as well. Like addition, the advantage of using two's complement is the elimination of examining the signs of the operands to determine if addition or subtraction is needed. For example, subtracting -5 from 15 is really adding 5 to 15, but this is hidden by the two's-complement representation:

Overflow is detected the same way as for addition, by examining the two leftmost (most significant) bits of the borrows; overflow has occurred if they are different.

Another example is a subtraction operation where the result is negative: 15 - 35 = -20:

```

11100 0000 (borrow)

0000 1111 (15)

- 0010 0011 (35)

```

As for addition, overflow in subtraction may be avoided (or detected after the operation) by first sign-extending both inputs by an extra bit.

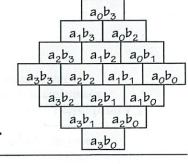

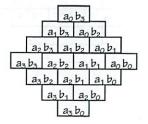

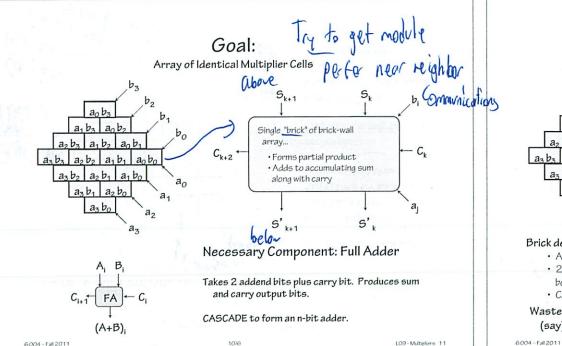

#### Multiplication

The product of two *n*-bit numbers requires 2n bits to contain all possible values. If the precision of the two two's-complement operands is doubled before the multiplication, direct multiplication (discarding any excess bits beyond that precision) will provide the correct result. For example, take  $6 \times -5 = -30$ . First, the precision is extended from 4 bits to 8. Then the numbers are multiplied, discarding the bits beyond 8 (shown by 'x'):

This is very inefficient; by doubling the precision ahead of time, all additions must be double-precision and at least twice as many partial products are needed than for the more efficient algorithms actually implemented in computers. Some multiplication algorithms are designed for two's complement, notably Booth's multiplication algorithm. Methods for multiplying sign-magnitude numbers don't work with two's-complement numbers without adaptation. There isn't usually a problem when the multiplicand (the one being repeatedly added to form the product) is negative; the issue is setting the initial bits of the product correctly when the multiplier is negative. Two methods for adapting algorithms to handle two's-complement numbers are common:

- First check to see if the multiplier is negative. If so, negate (i.e., take the two's complement of) both operands before multiplying. The multiplier will then be positive so the algorithm will work. Because both operands are negated, the result will still have the correct sign.

- Subtract the partial product resulting from the MSB (pseudo sign bit) instead of adding it like the other partial products. This method requires the multiplicand's sign bit to be extended by one position, being preserved during the shift right actions.<sup>[5]</sup>

As an example of the second method, take the common add-and-shift algorithm for multiplication. Instead of shifting partial products to the left as is done with pencil and paper, the accumulated product is shifted right, into a second register that will eventually hold the least significant half of the product. Since the least significant bits are not changed once they are calculated, the additions can be single precision, accumulating in the register that will eventually hold the most significant half of the product. In the following example, again multiplying 6 by -5, the two registers and the extended sign bit are separated by "|":

```

0 0110 (6) (multiplicand with extended sign bit)

× 1011 (-5) (multiplier)

01011010000

(first partial product (rightmost bit is 1))

01001110000

(shift right, preserving extended sign bit) (add second partial product (next bit is 1))

0|1001|0000

0|0100|1000

(shift right, preserving extended sign bit)

01010011000

(add third partial product: 0 so no change) (shift right, preserving extended sign bit)

0|0010|0100

1|1100|0100

(subtract last partial product since it's from sign bit)

(shift right, preserving extended sign bit) (discard extended sign bit, giving the final answer, -30)

11111010010

```

## Two's complement and universal algebra

In the classic "HAKMEM" published by the MIT AI Lab in 1972, Bill Gosper noted that whether or not a machine's internal representation was two's-complement could be determined by summing the successive powers of two. In a flight of fancy, he noted that the result of doing this algebraically indicated that "algebra is run on a machine (the universe) which is twos-complement." [6]

Gosper's end conclusion is not necessarily meant to be taken seriously, and it is akin to a mathematical joke. The critical step is "...110 = ...111 - 1", i.e., "2X = X - 1". This presupposes a method by which an infinite string of 1s is considered a number, which requires an extension of the finite place-value concepts in elementary arithmetic. It is meaningful either as part of a two's-complement notation for all integers, as a typical 2-adic number, or even as one of the generalized sums defined for the divergent series of real numbers  $1 + 2 + 4 + 8 + \cdots$ . [7]

# Potential ambiguities in usage

One should be cautious when using the term two's complement, as it can mean either a number format or a mathematical operator. For example 0111 represents 7 in two's complement notation, but 1001 is the two's complement of 7, which is the two's complement representation of -7. In code notation or conversation the statement "convert x to two's complement" may be ambiguous, as it could describe either the change in

representation of x to two's-complement notation from some other format, or else (if the writer really meant "convert x to its two's complement") the calculation of the negated value of x.

#### See also

- Division (digital), including restoring and non-restoring division in two's-complement representations

- Signed number representations

- p-adic numbers

- One's complement

- Offset binary

#### External links

- Tutorial: Two's Complement Numbers (http://www.vb-helper.com/tutorial twos complement.html)

- Two's complement array multiplier JavaScript simulator (http://www.ecs.umass.edu/ece/koren/arith /simulator/ArrMlt/)

#### References

- 1. ^ David J. Lilja and Sachin S. Sapatnekar, *Designing Digital Computer Systems with Verilog*, Cambridge University Press, 2005 online (http://books.google.com/books?vid=ISBN052182866X&id=5BvW0hYhxkQC&pg=PA37&lpg=PA37&ots=l-E0VjyPt8&dq=%22two%27s+complement+arithmetic%22&sig=sS5\_swrfrzcQI2nHWest75sIjgg)

- E.g. "Signed integers are two's complement binary values that can be used to represent both positive and negative integer values.", Section 4.2.1 in Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 1: Basic Architecture, November 2006

- $3. \ ^{\text{Reynald Affeldt and Nicolas Marti.}} \ ^{\text{Hormal Verification of Arithmetic Functions in SmartMIPS Assembly"} ( \ \text{http://www.ipl.t.u-tokyo.ac.jp/jssst2006/papers/Affeldt.pdf}). \ ^{\text{http://www.ipl.t.u-tokyo.ac.jp/jssst2006/papers/Affeldt.pdf}}.$

- 4. ^ "Digital Design and Computer Architecture" (http://books.google.com/books?id=5X7JV5-n0FIC&pg=PA19&dq=%22weird+number%22+binary) by David Harris, David Money Harris, Sarah L. Harris. 2007. Page 18.

- 5.  $^{\circ}$  John F. Wakerly, Digital Design Principles & Practices, Prentice Hall, 3rd edition 2000, page 47

- 6. ^ Hakmem Programming Hacks Draft, Not Yet Proofed (http://www.inwap.com/pdp10/hbaker/hakmem /hacks.html#item154)

- 7. ^ For the summation of 1 + 2 + 4 + 8 + · · · without recourse to the 2-adic metric, see Hardy, G.H. (1949). *Divergent Series*. Clarendon Press. LCC QA295 .H29 1967 (http://catalog.loc.gov/cgi-bin/Pwebrecon.cgi?Search\_Arg=QA295+.H29+1967& Search\_Code=CALL\_&CNT=5) . (pp. 7-10)

- Israel Koren, Computer Arithmetic Algorithms, A.K. Peters (2002), ISBN 1-56881-160-8

- Ivan Flores, The Logic of Computer Arithmetic, Prentice-Hall (1963)

Retrieved from "http://en.wikipedia.org/wiki/Two%27s\_complement" Categories: Computer arithmetic

- This page was last modified on 19 September 2011 at 22:01.

- Text is available under the Creative Commons Attribution-ShareAlike License; additional terms may apply. See Terms of use for details.

- Wikipedia® is a registered trademark of the Wikimedia Foundation, Inc., a non-profit organization.

| O to correct                                           |            |

|--------------------------------------------------------|------------|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | correct up |

| So if PHD to 3 For transmitting                        | l bit      |

| Can correct single bit errors                          |            |

| heads                                                  |            |

| tails                                                  |            |

| Just shap the are buch                                 |            |

| Review Section                                         |            |

| Detect D With errors HD > D                            |            |

| (orrect " " " MD > 20                                  |            |

| So I think I was Frinkly this - but prob made          | mistakes   |

- good to formalize

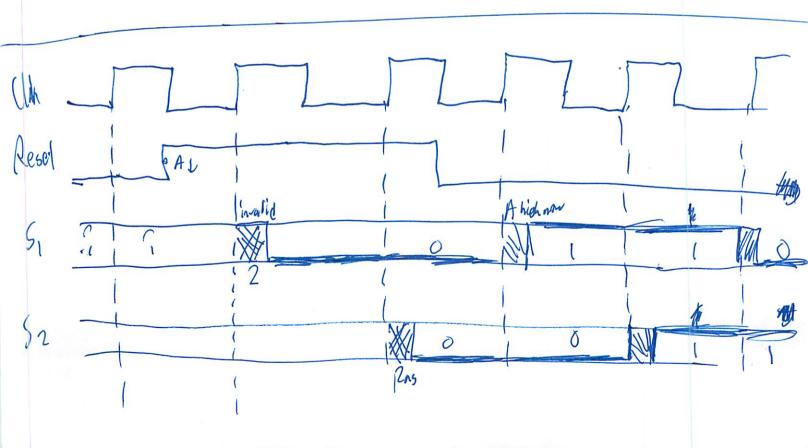

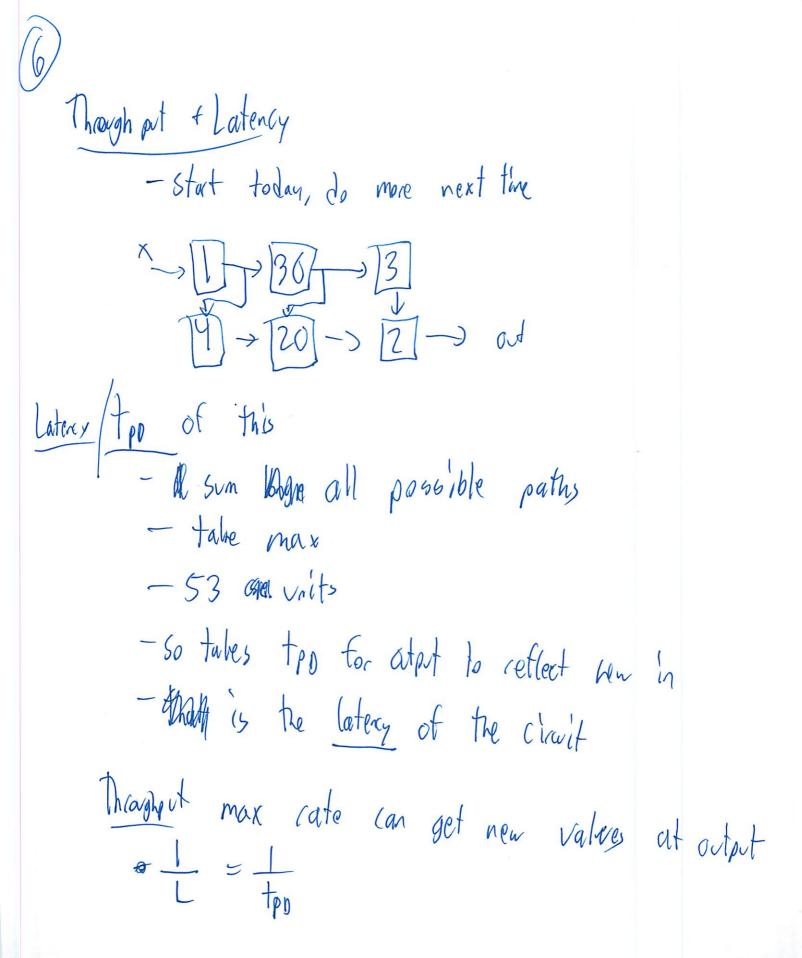

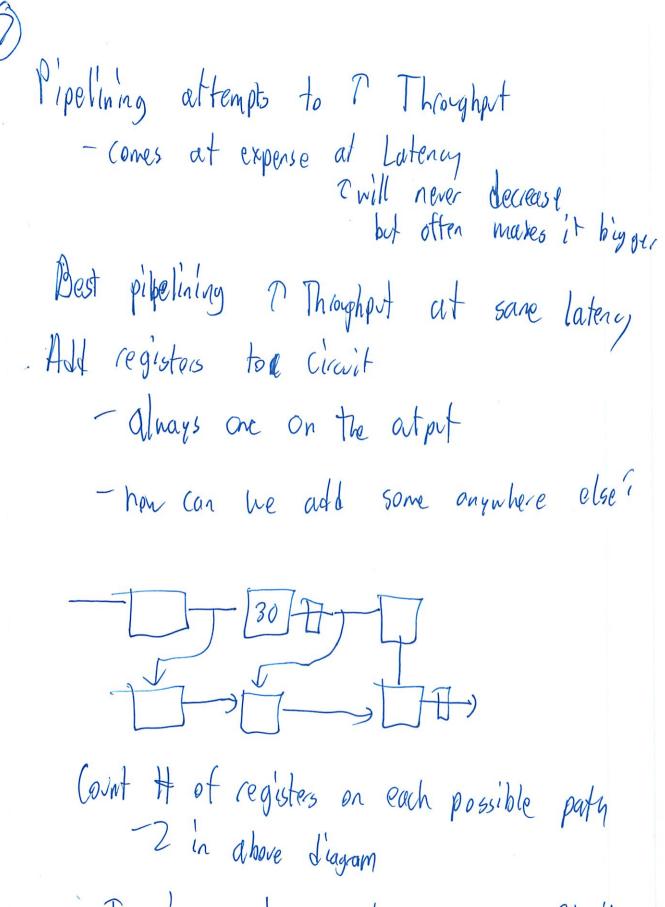

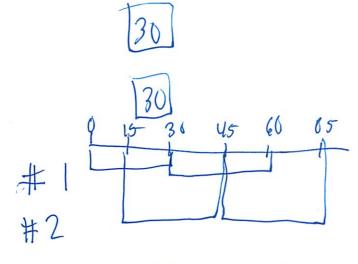

# Timing Review

What did I get wrong here's

Mostly analysis

Think Forgot exact specitics

— but I did cevier / write dam an cevier sheet

So CD is we start an invalid in to when out outstring invalid

PD is not Dated 2 pots our input has not become valid - how long for proper atput?

Renember

Why it is called a selector

A output,

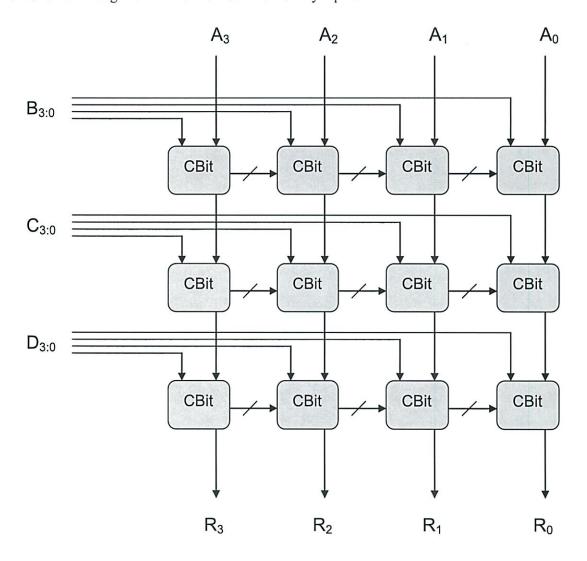

Then can make it bigger So Weeks 2 selectors need Toy(n) Selectos Out # = (A, 5, 5,)+(B, 5, 5,)+(C. 5, 5,)+(D, 5, 5,) Yole line TT! Bla Busically when  $5_0 = 0$   $5_1 = 0$  outputs A

Is made of combo of or gates

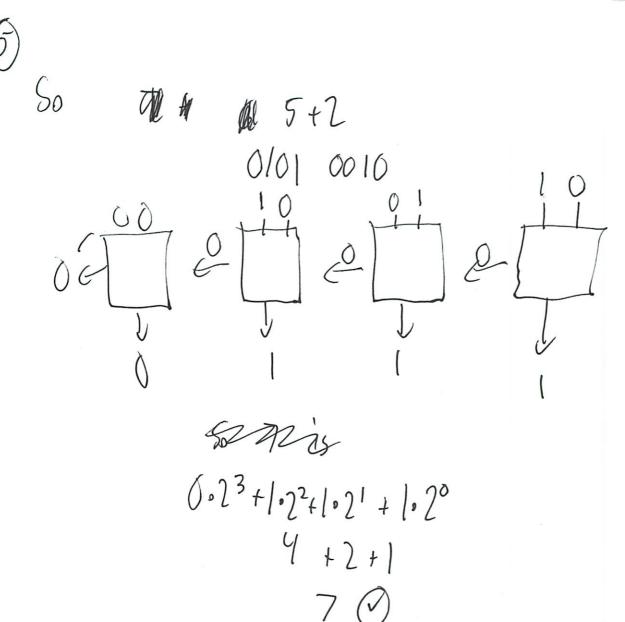

A - D - SI

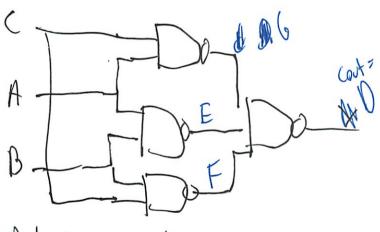

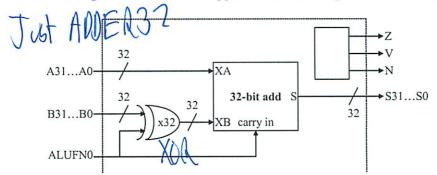

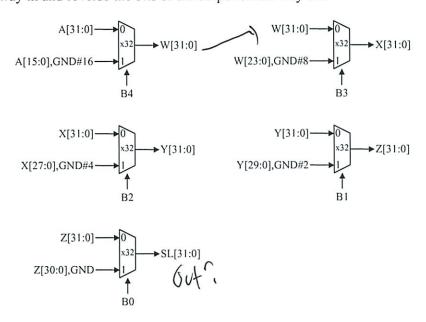

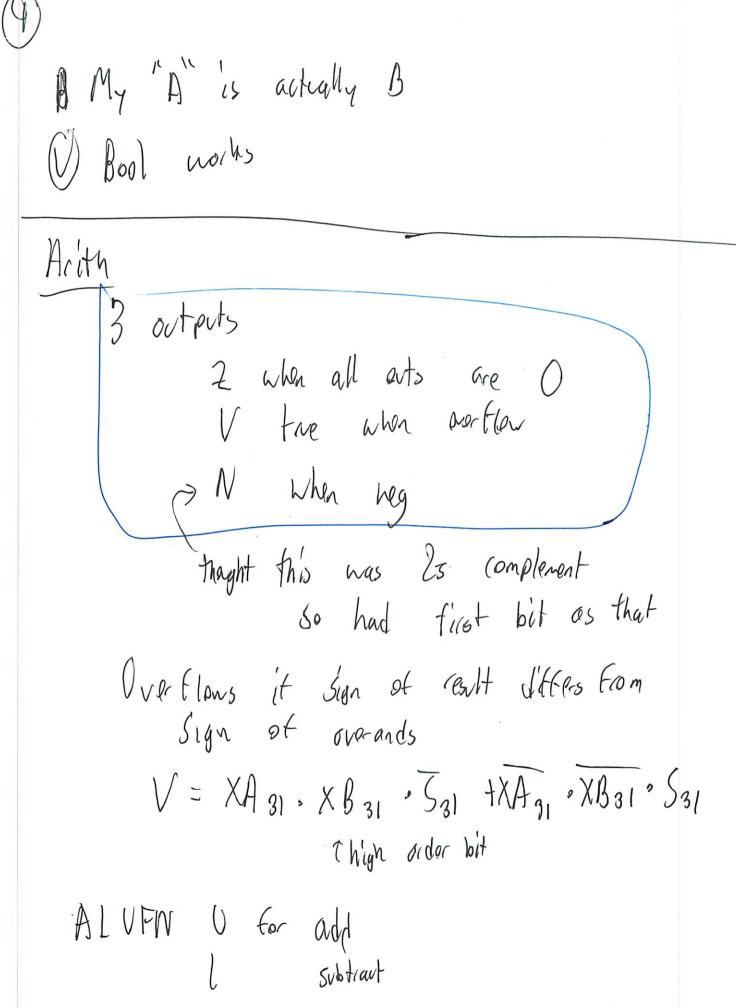

And Adder Strly

Adder - addiktion

- construt for your numeric representation

- binary coded decimal

- excess 3

- binary # Emost common

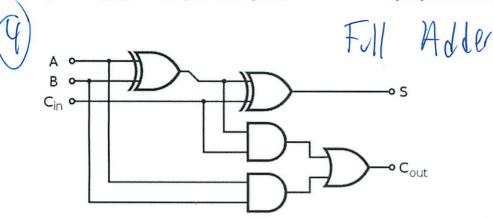

Malf adder - adds 2 1-bit # A, B -2 ats S, C = can cary - Sum is 2C+S

B (any Use Compositly

or borrow has been generated - allows

# 7 single ALV of least significant bit

back

255 + 255 - 510 for example 1111\_1116 (Special File) Of loits So ceturn IIII\_1110 + carry In 2's complement this is -1 +-1 =-2 (corect )

lets try A = 1 B = 1 S = |XOR| = 0 (= 1 ANO 1 = 1)

so what does this mean?

What is 2 in binary? Remember ealler 1.21+0.20 2 +0 60 10

50 males sense

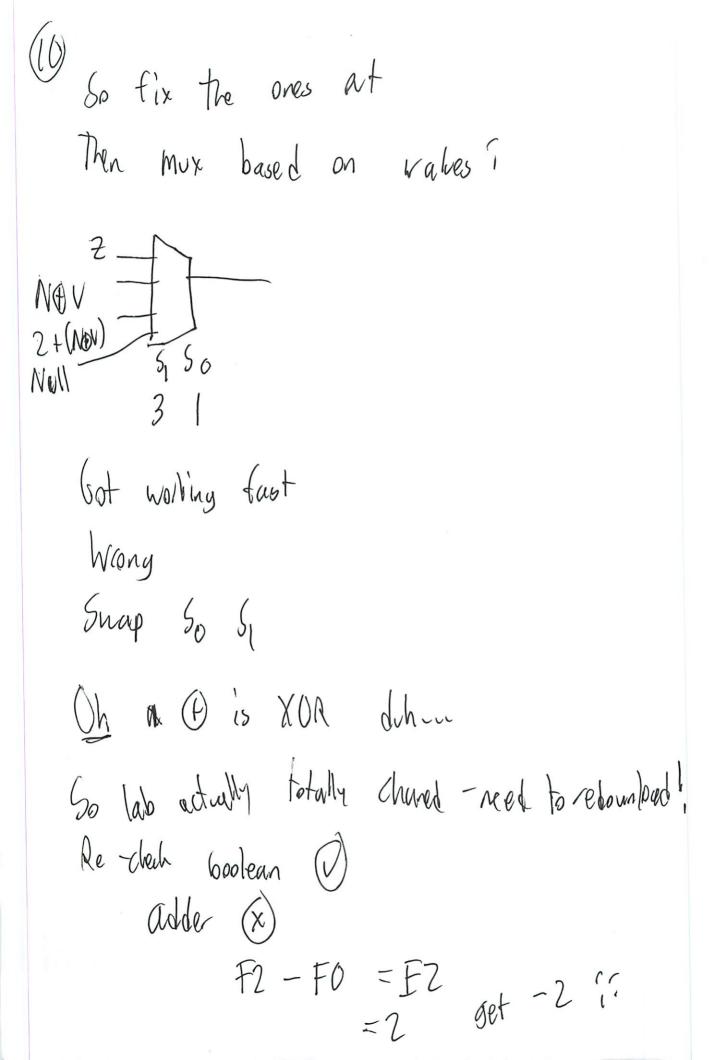

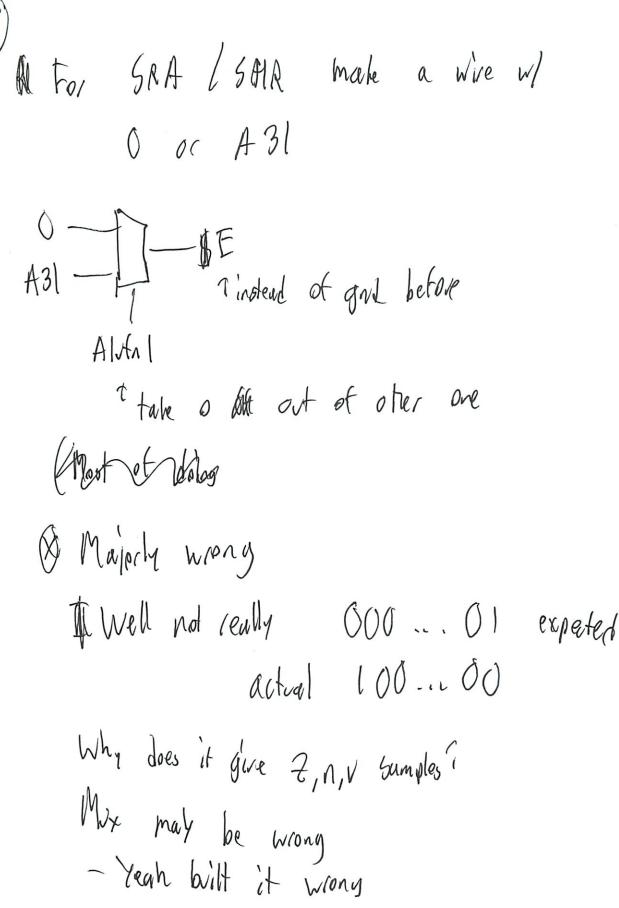

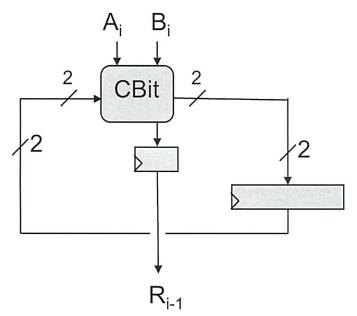

But then where is coury problem? Something about compositly

Full adder - Adds binnary # and keeps carries A PAM" I bit full adder has 3 inputs A ) operand C - carried in from previous This is difference here (an string trem tayeter what if voing half A = 1 S = 0 Q = 1 S = 6 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q = 1 Q =but what about bit positions and where sids go 2,1 +0 Look at how Ell is different. Still 26+5

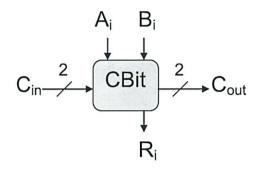

$S = A \oplus B \oplus C_{in}$   $Cox = (A \cdot B) + (C_{in} \cdot (A \oplus B))$   $Cox = (A \cdot B) \oplus (C_{in} \cdot (A \oplus B))$   $Cox = (A \cdot B) \oplus (C_{in} \cdot (A \oplus B))$

AND/OR gates can be replaced ul NANO For some

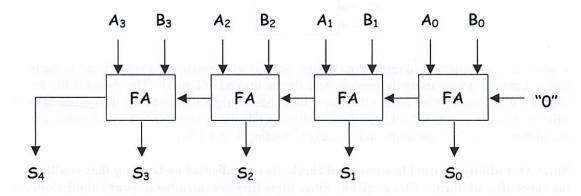

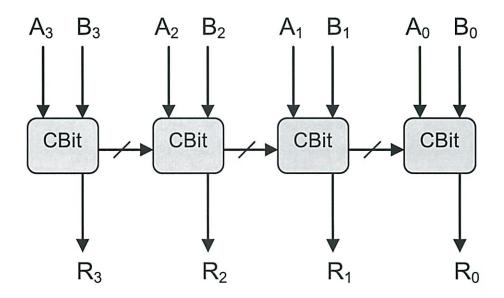

Ripple Adder

Use multiple fill adders to add N-bit #

The Cin is the previous Carl

Vinda Sow

- 32 bit so worst case

3102 +3 -65 gate delays

To gress each bit one at a fine

- n-to-n2 more complex

Op to max n2

but some may be unvold

The decoder we looked at early as part of encoder

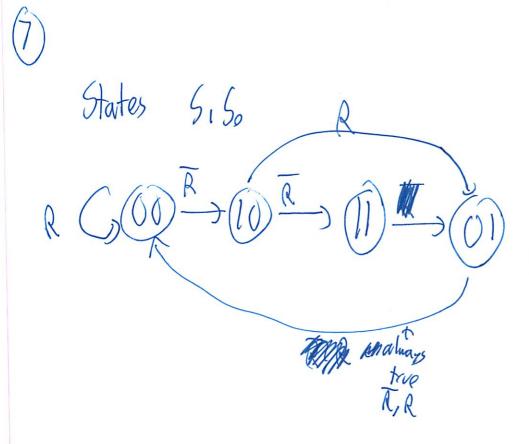

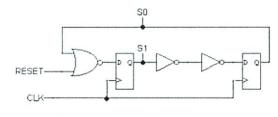

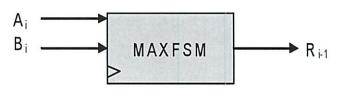

# (Synchronous) Finite State Machines

Lab 2 is due Thursday!

6.004 - Fall 2011

6.004 - Fall 2011

9/27

modified 9/26/11 10:51

LOG-FSMs 1

LOG-FSMs 3

# Must Respect Timing Assumptions!

We know how fast it goes ... But what can it do? Timbo

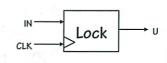

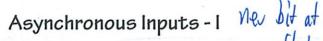

# A simple sequential circuit...

Lets make a digital binary Combination Lock:

- · One input ("O" or "1") String of bits

- · One output ("Unlock" signal)

- UNLOCK is 1 if and only if:

How many registers do Ineed?

Last 4 inputs were the "combination": 0110

How much state to save"

6.004 - Fall 2011

9/27

LOG-FSMs 4

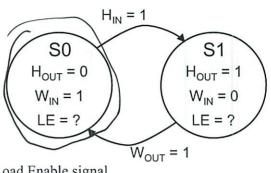

# Abstraction du jour: Finite State Machines

### · A FINITE STATE MACHINE has

- · k STATES: S<sub>1</sub> ... S<sub>k</sub> (one is "initial" state)

- · m INPUTS: 1, ... 1,

- · n OUTPUTS: 0, ... 0.

Transition Rules: s'(s, I) for each state s and input I

Output Rules: Out(s) for each state s

6.004 - Fall 2011

LOG-FSMs 5

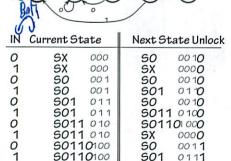

# Yet Another Specification

501 The assignment of codes to states can be arbitrary, however, if you choose them carefully you

All state transition diagrams can be described by truth tables...

Binary encodings are assigned to each state (a bit of an art)

The truth table can then be simplified using the reduction techniques we learned for combinational

Map of functionality

State Transition Diagram resct Heavy circle Designing our lock ... Means INITIAL state NAME · Need an initial state: call it SX. ofstate · Must have a separate state for each step XXX of the proper entry sequence OUTPUT · Must handle other (erroneous) entries causina when in this transition state

6.004 - Fall 2011

9/27

LOG-FSMs 6

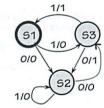

# Valid State Diagrams

MOORE Machine: Outputs on States

MEALY Machine: Outputs on Transitions

- Arcs leaving a state must be:

- (1) mutually exclusive

- can't have two choices for a given input value

- (2) collectively exhaustive

- every state must specify what happens for each possible input combination. "Nothing happens" means arc back to itself.

LOG-FSMs B

6.004 - Fall 2011

6.004 - Fall 2011

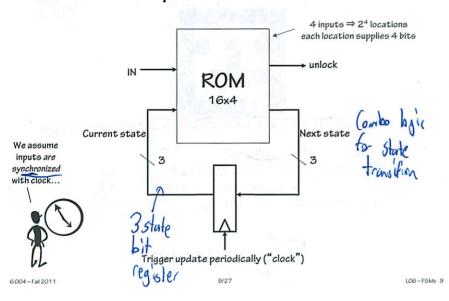

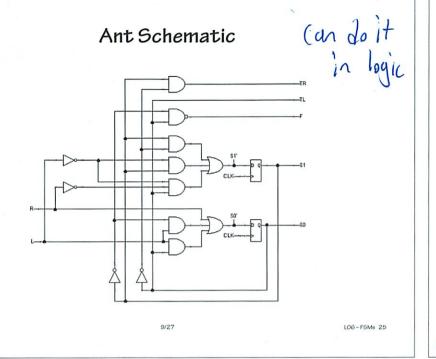

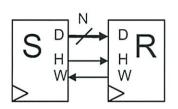

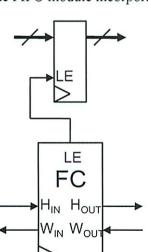

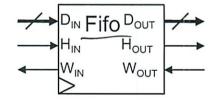

# Now put it in Hardware!

### Discrete State, Time

6.004 - Fall 2011

6004 - Fall 2011

9/27

LOG - FSMs 10

31Lock

But what About the

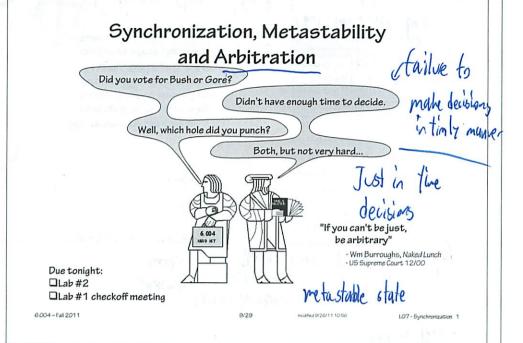

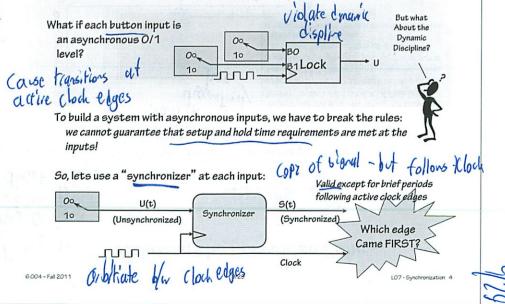

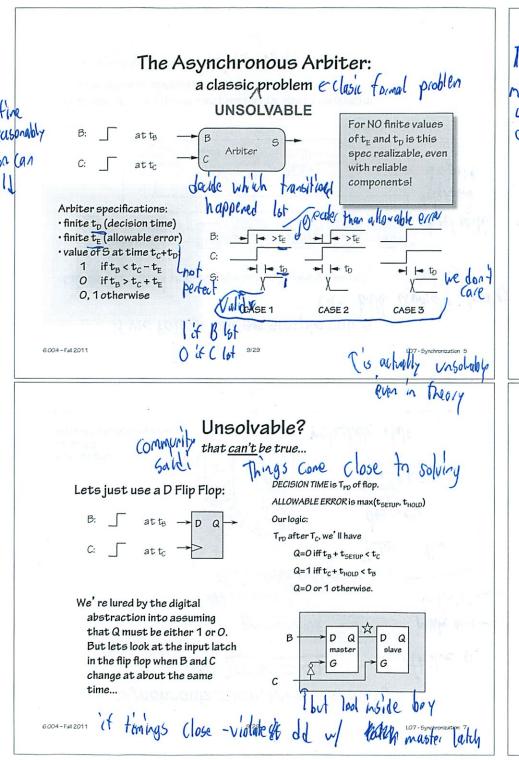

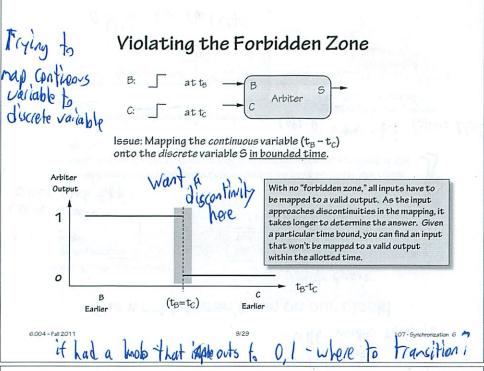

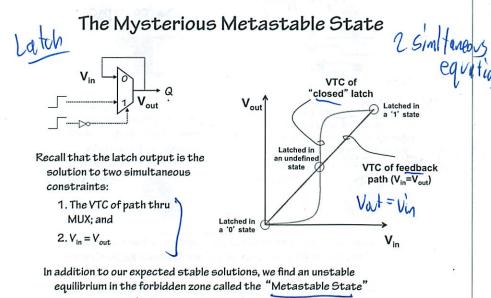

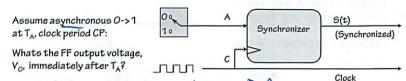

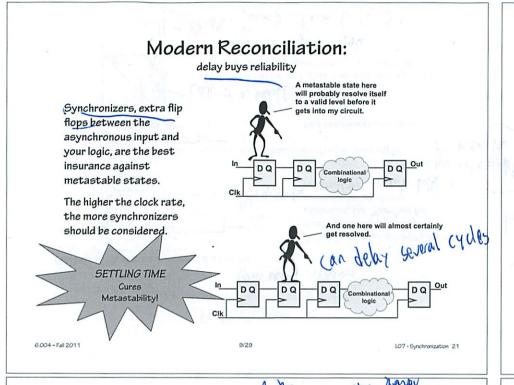

Our example assumed a single clock transition per input. What if the "button pusher" is unaware of, or not synchronized with, the clock?

What if each button input is an asynchronous O/1 level? How do we prevent a single button press, e.g., from making several transitions?

Use intervening states to synchronize button presses!

6.004 - Fall 2011

9/2

LOG-F5Ms 11

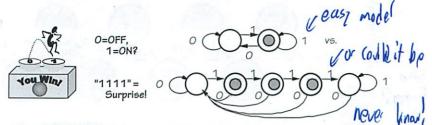

# FSM Party Games

1. What can you say about the

number of states?

2. Same question:

2 mon

3. Here's an FSM. Canyou discover its rules?

not in general cust

LOG-F5Ms 12

# What's My Transition Diagram?

- If you know NOTHING about the FSM, you're never sure!

- If you have a BOUND on the number of states, you can discover its behavior:

K-state FSM: Every (reachable) state can be reached in < k steps.

BUT ... states may be equivalent!

6.004 - Fall 2011

9/27

LOG-F5Ms 13

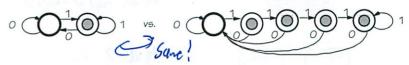

# FSM Equivalence

ARE THEY DIFFERENT?

NOT in any practical sense! They are EXTERNALLY INDISTINGUISHABLE, hence interchangeable.

FSMs EQUIVALENT iff every input sequence yields identical output sequences.

#### ENGINEERING GOAL:

- · HAVE an FSM which works...

- WANT <u>simplest</u> (ergo cheapest) equivalent FSM.

6.004 - Fall 2011

6004 - Fall 2011

1-57 use cheaper -it equivilant

LOG-F5Ms 14

# Lets build an Ant

- SENSORS: antennae L and R, each 1 if in contact with something.

- ACTUATORS: Forward Step F, ten-degree turns TL and TR (left, right).

GOAL: Make our ant smart enough to get out of a maze like:

STRATEGY: "Right antenna to the wall"

6.004 - Fall 2011

9/2

LOG-FSMs 15

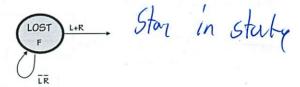

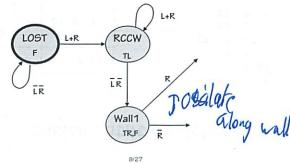

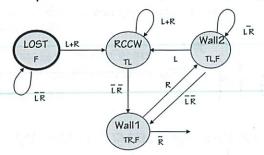

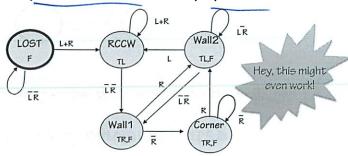

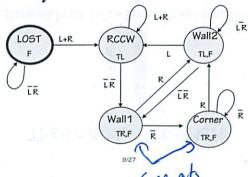

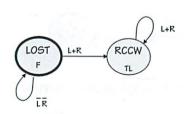

# Lost in space

Action: Go forward until we hit something.

"lost" is the initial state

9/2

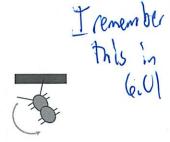

LOG-FSMs 16

### Bonk!

A little to the right...

Action: Step and turn right a little, look for wall

6.004 - Fall 2011

LOG-FSMs 18

Action: Turn left (CCW) until we don't touch anymore

6.004 - Fall 2011

6.004 - Fall 2011

9/27

LOG-FSMs 17

### Then a little to the left

Action: Step and turn left a little, till not touching (again)

LOG-F5Ms 19

Dealing with corners

Action: Step and turn right until we hit perpendicular wall

6.004 - Fall 2011

9/27

LOG-F5Ms 20

# Can we simplify it is Equivalent State Reduction

Observation: S, ≅ S, if

- 1. States have identical outputs; AND

- 2. Every input ⇒equivalent states.

look for equivilant

Reduction Strategy:

Find pairs of equivalent states, MERGE them.

Same outs

LOG-FSMs 21

me190

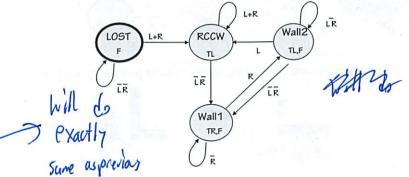

# An Evolutionary Step

Merge equivalent states Wall 1 and Corner into a single new, combined state.

Behaves exactly as previous (5-state) FSM, but requires half the ROM in its implementation!

6.004 - Fall 2011

6.004 - Fall 2011

9/27

LOG - FSMs 22

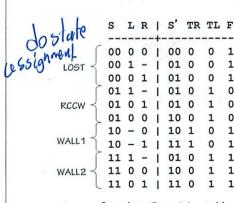

# Building the Transition Table

pt together trans touble

| S  | т. | R | 1  | s' | TВ | TL | F |  |

|----|----|---|----|----|----|----|---|--|

|    |    |   | +- |    |    |    |   |  |

| 00 | 0  | 0 | 1  | 00 | 0  | 0  | 1 |  |

| 00 | 1  | _ | 1  | 01 | 0  | 0  | 1 |  |

| 00 | 0  | 1 | 1  | 01 | 0  | 0  | 1 |  |

| 01 | 1  | - | 1  | 01 | 0  | 1  | 0 |  |

| 01 | 0  | 1 | 1  | 01 | 0  | 1  | 0 |  |

|    |    |   | 1  |    |    |    |   |  |

|    |    |   | 1  |    |    |    |   |  |

|    |    |   | 1  |    |    |    |   |  |

|    |    |   | 1  |    |    |    |   |  |

|    |    |   | 1  |    |    |    |   |  |

# Implementation Details

Complete Transition table

s1' 00 01 11 10 11 0 0  $S_1' = S_1 \overline{S_0} + \overline{L} S_1 + \overline{L} R S_0$  $S_0' = R + L\overline{S_1} + LS_0$

LOG-FSMs 24

6004 - Fall 2011

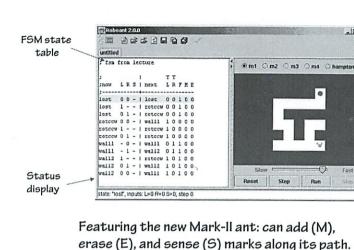

Did we all descend from FSMs???

Maze

Plan view

of maze

Simulation

controls

selection

6.004 - Fall 2011

# async clear

- 1. Initialization? Clear the memory?

- 2. Unused state encodings?

- waste ROM (use PLA or gates)

- what does it mean?

- can the FSM recover?

- 3. Choosing encoding for state? State assignants

- state update?

4. Synchronizing input changes with 900 for

Now, that's a funny looking state machine

# Twisting you Further...

9/27

Roboant®

MORE THAN ANTS:

6.004 - Fall 2011

Swarming, flocking, and schooling can result from collections of very simple FSMs

- PERHAPS MOST PHYSICS: Cellular automata, arrays of simple FSMs. can more accurately model fluilds than numerical solutions to PDEs

- · WHAT IF: We replaced the ROM with a RAM and have outputs that modify the RAM?

- ... You'll see FSMs for the rest of your life!

the lit on This

I prefer to think we

LOG-FSMs 28

- 1 Cevitation per lecture -so a bit behind Today: Building look of CMUS So troth table - Jothragh each possible input -try each row -fill in w/ percil

A B 2 -slow + plodding D-NAM - Ninputs = 2 Nortputs

2(2N) possible TT (ons

possible gates w/ N inputs

(given for 2 on slides)

Turniary look 2 inputs

| Alba Pertorance                                                                  | Valid atput of 1                                 |               |

|----------------------------------------------------------------------------------|--------------------------------------------------|---------------|

| Shorthard I<br>NAMD > ND2<br>AND > AH2<br>12<br>NDQ > NA2<br>5<br>12<br>OR > OR2 | tpo tr tf  15 8 57 30 11 9 50 13 9 50 13 9 50 13 | each date     |

|                                                                                  |                                                  | e Nor get for |

Z Whole system

to = Minimum of all paths

-hot just of visually shortest path!

So Calulate Cach

-add along each possible car

B 15t5 t5 = 115 Contreed

12+5+5=22

inverter one

Since will be

longer than the

One above it

tpd - now looking for longest

- innumerate each one again, sum

- using tpd

- \( \sum\_{tpd} \)

The totall

When 2 goes 0 - 1

That case about gate the atput is hooked to last

Coince this not looks at output

ty = invalled in to invalid net too short lawill be a problem ta to valid in y valid at to valid 1 > valid 0 to cease to for tr

Now the cerese. Get truth table. (6) Brild cirwit. This is priority empder -like interpt circuit ABCIPOPI 010 () mono 1 10 100/114 101 110 Now instead of drawing gates, write expression Each cow of IT represents product term (did in class) Flost cow A.B.C SO AND(AND(A,B),C)

| Then or                               | together                        | all the        | results | that    | ore   | 1  | For | Pu |

|---------------------------------------|---------------------------------|----------------|---------|---------|-------|----|-----|----|

|                                       | ABC<br>ABC<br>ABC<br>ABC<br>ABC | (or write w/t) | -> Po   | (epea   | t for | Pi |     |    |

| Cold a                                | lso Cascai                      | le it U        |         |         |       |    |     |    |

| X X X X X X X X X X X X X X X X X X X | X4                              |                |         |         |       |    |     |    |

| But                                   | slower it                       | all inputs     | achel   | at same | , ti  | ų  |     |    |

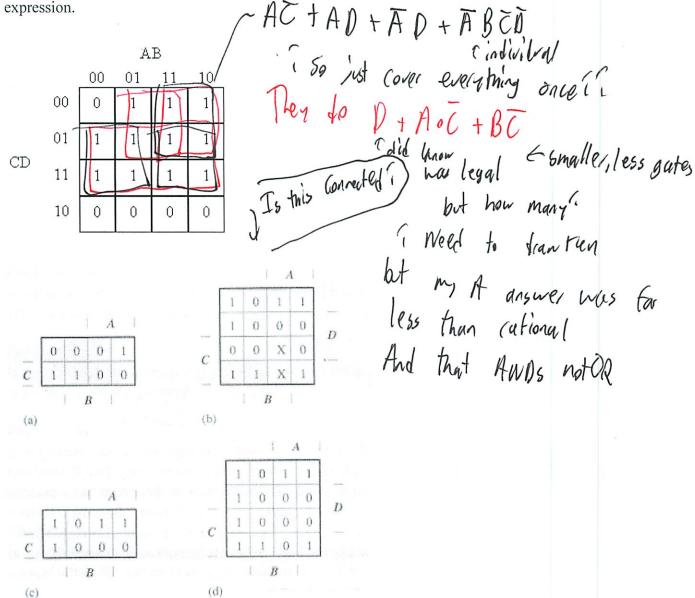

But slower it all inputs acriel at some time becomes important in lab 3 Now can you to it w/ less gates First can baild don't care TTs since ABC = ABC = ABC = ABCall some afort just Say A - -Can represent as fauto  $\overline{A}$   $B(\overline{C}+C) = \overline{A}B$ Can do w/ table - " k-maps" - " Marnargh" Specific e-fill in from T LOOPS bown

Good for up to 4 nodes

(an have patches of 612es: 1 x 2 2 x 1 2 \* 2 4 x 1 1 x 4 4x4 Think of longent patches can circle - Overlapping is that fine > key to success Value of Colors not matter

Value of B = 1

A does not matter

That read So for 4s A+B chow did no

Meat this On your own I ROM

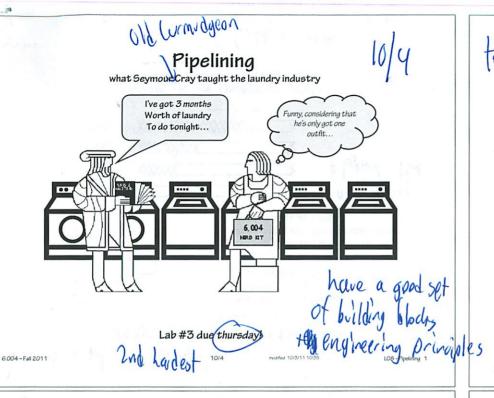

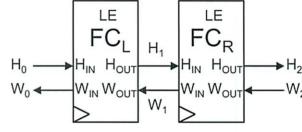

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

### 6.004 Computation Structures Lab #2

### Introduction

Read 9/24

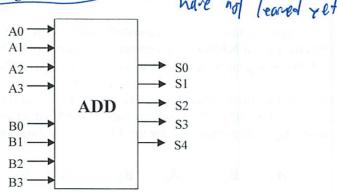

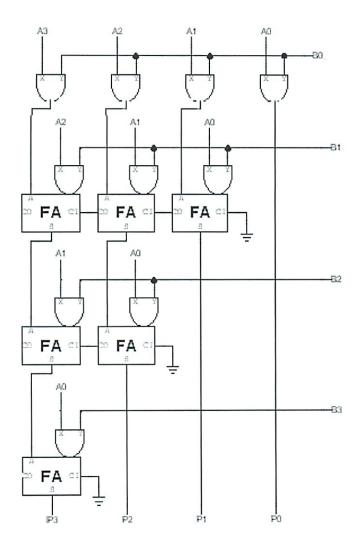

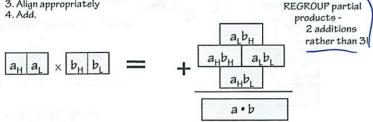

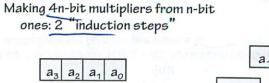

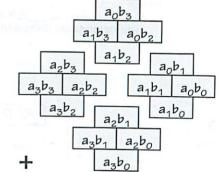

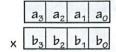

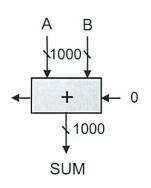

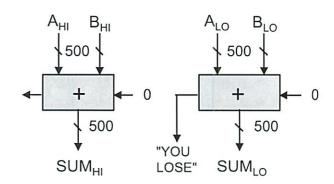

Your mission this week is to design and test a CMOS circuit that performs addition on two unsigned 4-bit numbers, producing a 5-bit result:

When you've completed and tested your design, you can ask JSim to send your circuit to the online assignment system using the process described at the end of Lab #1. The checkoff file for Lab #2 (lab2checkoff.jsim) checks that your circuit has the right functionality; the on-line system will give you 5 points for checking off your lab using this file. (You'll receive your points after completing the on-line questions and a checkoff meeting with a TA.)

Note: Our ability to provide automated checkoffs is predicated on trusting that you'll use the checkoff and library files as given. Since these files are included in your submission, we will be checking to see if these files have been used as intended. Submittals that include modified checkoff or library files will be regarded as a serious breach of our trust and will be dealt with accordingly.

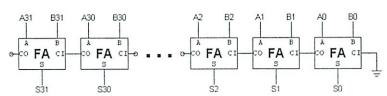

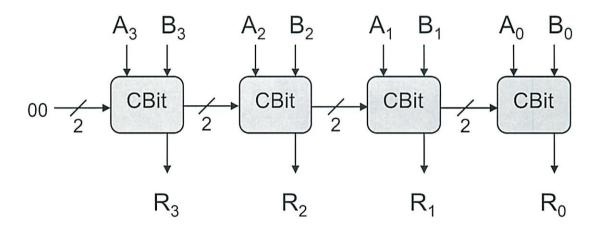

# 1: Ripple Adders

Let's start with a simple ripple-carry adder based on the full-adder module discussed in lecture. Later we'll discuss higher performance adder architectures you can use in the implementation of the Beta (the computer central processing unit we'll be designing in later labs).

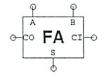

The full adder module has 3 inputs (A, B and  $C_i$ ) and 2 outputs (S and  $C_o$ ). The logic equations and truth table for S and  $C_o$  are shown below.

y and my

$$S = A \oplus B \oplus C_{in}$$

$C_o = A \cdot B + A \cdot C_{in} + B \cdot C_{in}$

|   | C; | АВ  | S C. | ennavo"Venora                                |

|---|----|-----|------|----------------------------------------------|

| _ | 0  | 0 0 | 0 0  | A D                                          |

|   | 0  | 0 1 | 1 0  | da.l AB                                      |

|   | 0  | 1 0 | 1 0  | * *                                          |

|   | 0  | 1 1 | 0 1  | $C_{\bullet} \leftarrow FA \leftarrow C_{i}$ |

|   | 1  | 0 0 | 1 0  | ***************************************      |

|   | 1  | 0 1 | 0 1  | ζ.                                           |

|   | 1  | 1 0 | 0 1  | A live of but the poly                       |

|   | 1  | 1 1 | 1 1  |                                              |

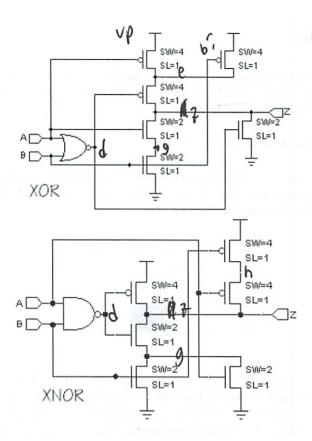

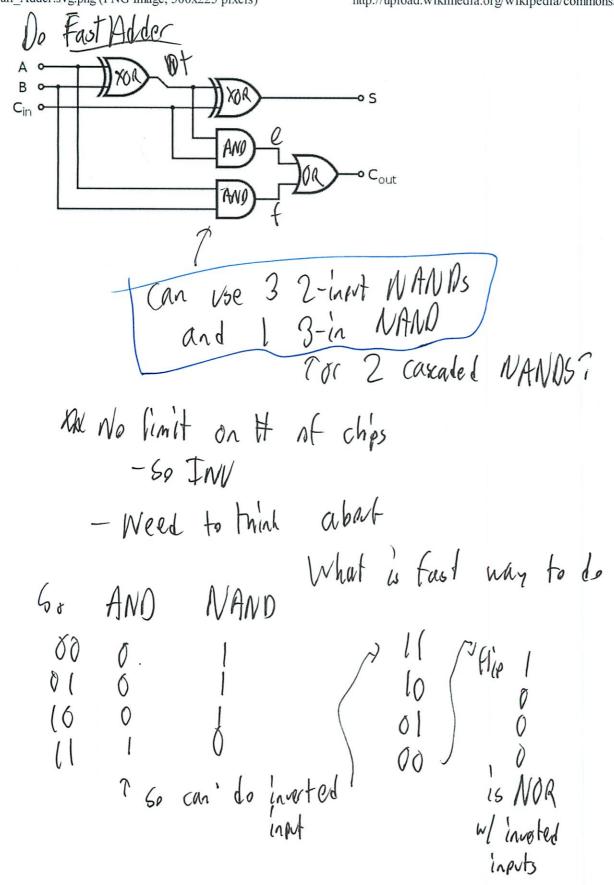

Typically S is implemented using two cascaded 2-input XOR gates. One can use three 2-input NANDs and one 3-input NAND to implement  $C_o$  (remember that by Demorgan's Law two cascaded NANDs is logically equivalent to a cascade of AND/OR).

The module performs the addition of two one-bit inputs (A and B) incorporating the carry in from the previous stage  $(C_i)$ . The result appears on the S output and a carry  $(C_o)$  is generated for the next stage. A possible schematic for the 4-bit adder is shown below:

### 2: XOR/XNOR Gates

they shalp They bright

Since we're using individual gates to implement the logic, a good place to start is to build your own gate library (e.g., inverter, 2-input NAND, 2-input NOR, 2-input XOR), test them individually, and then use them to implement your design. It's much easier to debug your circuit module-by-module rather than as one big lump. XOR/XNOR can be challenging gates to design; here's one suggestion for how they might be implemented:

" (an copy from last week

### 3: Generating Test Signals

You can use voltage sources with either a pulse or piece-wise linear waveforms to generate test signals for your circuit (see Lab #1 for details). Another source of test waveforms is the file "/mit/6.004/jsim/8clocks.jsim" which can be included in your netlist. It provides eight different square waves (50% duty cycle) with different periods:

```

clk1

period = 10ns

clk2

period = 20ns

clk3

period = 40ns

clk4

period = 80ns

clk5

period = 160ns

clk6

period = 320ns

clk7

period = 640ns

clk8

period = 1280ns

```

For example, to completely test all possible input combinations for a 2-input gate, you could connect clk1 and clk2 to the two inputs and simulate for 20ns.

### 4: Plotting Results

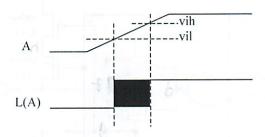

Interpreting analog signal levels as logic values can be tedious. JSim will do it for you automatically if you ask to plot "L(a)" instead of just "a". The logic-high and logic-thresholds are determined by the "vih" and "vil" options:

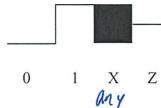

Initial values are specified in "/mit/6.004/jsim/nominal.jsim", but you can respecify them in your own netlist. Voltages between vil and vih are displayed as a filled-in rectangle to indicate that the logic value cannot be determined. For example:

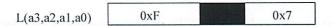

You can also ask for the values of a set of signals to be displayed as a bus, e.g., "L(a3,a2,a1,a0)". The signals should be listed most-significant bit first. A bus waveform is displayed as a filled-rectangle if any of the component signals has an invalid logic level or as a hexadecimal value otherwise. In the following plot the four signals a3, a2, a1 and a0 are interpreted as a 4-bit integer where the high-order bit (a3) is making a  $1\rightarrow 0$  transition. The filled-in rectangle represents the period of time during which a3 transitions from  $V_{IH}$  to  $V_{IL}$ .

### 5: Design Guidelines

Here's a list of design tasks you might use to organize your approach to the lab:

- 1. Draw a gate-level schematic for the full-adder module. XOR gates can be used to implement the S output; two levels of NAND gates are handy for implementing  $C_{\text{o}}$  as a sum of products.

- 2. Create a MOSFET circuit for each of the logic gates you used in step 1.

- 3. Enter .subckt definitions in your netlist for each of the logic gates. Use Jsim to test each logic gate with all possible combinations of inputs. Debugging your gate designs one-by-one will be much easier than trying to debug them as part of the adder circuit. Here's a sample netlist for testing a 2-input NAND gate called nand2:

```

.include "/mit/6.004/jsim/nominal.jsim"

.include "/mit/6.004/jsim/8clocks.jsim"

```

```

.subckt nand2 a b z

... internals of nand2 circuit here

.ends

Xtest clk1 clk2 z nand2

.tran 20ns

.plot clk1

.plot clk2

.plot z

```

- 4. Enter a .subckt definition for the full-adder, building it out of the gates you designed and tested above. Use Jsim to test your design with all 8 possible combinations of the three inputs. At this point you probably want to switch to using "Fast Transient Analysis" do to the simulations as it is much faster than "Device-level Simulation".

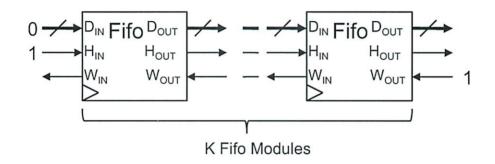

- 5. Enter the netlist for the 4-bit adder and test the circuit using input waveforms supplied by lab2checkoff.jsim. Note that the checkoff circuitry expects your 4-bit adder to have exactly the terminals shown below the inside circuitry is up to you, but the ".subckt ADDER4..." line in your netlist should match exactly the one shown below.

```

.include "/mit/6.004/jsim/nominal.jsim"

.include "/mit/6.004/jsim/lab2checkoff.jsim"

... subckt definitions of your logic gates

.subckt FA a b ci s co

... full-adder internals here

.ends

.subckt ADDER4 a3 a2 a1 a0 b3 b2 b1 b0 s4 s3 s2 s1 s0

* remember the node named "0" is the ground node

* nodes c0 through c3 are internal to the ADDER module

Xbit0 a0 b0 0 s0 c0 FA

Xbit1 a1 b1 c0 s1 c1 FA

Xbit2 a2 b2 c1 s2 c2 FA

Xbit3 a3 b3 c2 s3 s4 FA

.ends

```

lab2checkoff.jsim contains the necessary circuitry to generate the appropriate input waveforms to test your adder. It includes a .tran statement to run the simulation for the appropriate length of time and a few .plot statements showing the input and output waveforms for your circuit.

When debugging your circuits, you can plot additional waveforms by adding .plot statements to the end of your netlist. For example, to plot the carry-out signal from the first full adder, you could say

```

.plot Xtest.c0

```

where Xtest is the name lab2checkoff.jsim gave to the ADDER4 device it created and c0 is the name of the internal node that connects the carry-out of the low-order FA to the carry-in of the next FA.

6.004 Lab 2

Brild adder

- 2 4-bit unsigned #

Oh researched this this weekend

So will gates

- Vid we not do this last time?

NAND, Inverter

NOR

- try to lo self

- or look in lecture notes

-no do self

Since of Since of the same of

How to fest? Test later Now wild XOR - trey tell us hon Weed to convert -looks complicated Mour do you come up ut Mese ?? Tested inverter (V) Ther gave instructions later NANDZ AND NAND WORZ

No - does not work! ()h e=2 Needed to do Fast analysis? 00 | 1 ~ (Invert ofter XOR output?

01 0/ O works

(I an Winda shortutting lab i know my way

C Jinv & NOA same out

A SIN SI

Bow AMA OR 000 in 8 00 1 fill 1 Cinvet all and NAND e > (nv -> h f > (nv -> h This will be for many gates Most be eauer my - W DO D Ok test that CABISC

Non I reed to put them tegether - almost Forgot Now read how they are specing it Oh can have multiletter hodes Thy even tell you have they open do it Deplicate device name when try to run test Oh included file twice (duh) - it shald know this Plot is really inread able! BA passed ventication ()

Now avestions + meeting

- That took 1.5 his

(Do to morrow

lab 2 Chechot Cascading ANDs into ORs > (an Use NOR (an bill 3-input NAM) boing to need to optimize Redo - fix critical path Since need to use it later - lab le

Ocheded off

### 6.004 On-line: Questions for Lab 2

When you're done remember to save your work by clicking on the Save'button at the bottom of the page. You can check if your answers are correct by clicking on the Check'button.

When entering numeric values in the answer fields, you can use integers (1000), floating-point numbers (1000.0), scientific notation (1e3), or JSim numeric scale factors (1K).

<u>Problem 1.</u> The following questions are multiple-choice. Using the "check" button, you can of course simply keep guessing until you get the right answer. But you'll be in a much better position to take the quizzes if you take the time to actually figure out the answers.

A. If we set the inputs of a particular CMOS gate to voltages that correspond to valid logic levels, we would expect the *static* power dissipation of the gate to be

non-zero, but very small (picowatts)

B. Measuring a particular CMOS device G, we find 1.5V noise margins. If the *width* of all mosfets inside of G were doubled, we would expect the noise margins of the new gate to

stay about the same

C. To decrease the output rise time of a CMOS gate one could

increase the width of all pfets

D. Suppose one wanted to *decrease* the propagation time of a CMOS circuit. Which of the following actions would lead to the greatest possible speed up?

increase the power supply voltage and lower the operating temperature

Problem 2. Almost all of the power dissipated by CMOS circuits goes into charging and discharging nodal capacitances. This power can be computed as  $C(V^2)F$  where C is the capacitance being switched, V is the change in voltage, and F is the frequency at which the switching happens. In CMOS circuits, nodes are switched between ground (0 volts) and the power supply voltage

(VDD volts), so V is either +VDD or -VDD and so  $V^2$  is  $VDD^2$ .

A. Suppose we have a device implemented in a technology where VDD = 5V. If we have the option of reimplementing the device in a technology where VDD = 3.3V, what sort of speedup (i.e., change in F) could be specified for the reimplementation assuming we want to keep the power budget unchanged?

Speedup (eg, 2.0 would be twice as fast): 2.29

<u>Problem 3.</u> As we saw in Lecture 4, there are 16 possible 2-input combinational logic gates. The cost of implementing these gates varies dramatically, requiring somewhere between 0 and 10 mosfets depending on the gate. For example, it takes 2 mosfets to implement "F = NOT A", but 4 mosfets (organized as two inverters) to implement "F = A".

For each of the 2-input gates whose Karnaugh maps are given below, indicate the minimum number of mosfets required to implement the gate. You should only consider static fully-complementary circuits like those shown in lecture; these implementations meet the following criteria:

- no static power dissipation

- Vol = 0V, Voh = power supply voltage

- Nfets appear only in pulldown paths, Pfets appear only in pullup paths

- the pullup and pulldown are complementary, i.e., when one path is "on", the other is "off"

- the pullup and pulldown circuits can be decomposed into series and parallel connections of mosfets

- all gate implementations restore incoming logic levels (so a wire connecting an input terminal to an output terminal would not be a legal gate implementation)

So A=1, B varies so A since A supposed to be 1

B So A+B+AB but the 1;

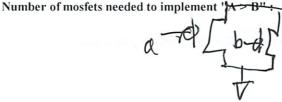

Number of mosfets needed to implement "NOR":

B.

|    | ID | A | 1 |

|----|----|---|---|

| AN | עו | 0 | 1 |

| D  | 0  | 0 | 0 |

| В  | 1  | 0 | 1 |

NAND = 4 + inverter = 5 & No need to invert in Not out 6

Number of mosfets needed to implement "AND":

# 6

C.

| XN  | OΒ | A | 4 |

|-----|----|---|---|

| AIN | OK | 0 | 1 |

| _   | 0  | 1 | 0 |

| В   | 1  | 0 | 1 |

See p-sel

Number of mosfets needed to implement "XNOR":

6 + NAND Y

D.

| NO | тр | F | 4 |

|----|----|---|---|

| NO | IB | 0 | 1 |

|    | 0  | 1 | 1 |

| В  | 1  | 0 | 0 |

So don't care A

But how to dred it B true -OLF

2

Number of mosfets needed to implement "NOT B":

F

Check

Save

a) (MOS valid inputs Static power -> 6 or need 0 b) doubling width noise marging - no clue star the same () -its speel () to I output clise time double w but for which pullup pa-fet r-d cenember "np" O > 1 60 d) I prop time -oh a) power supply v + opp temp Mand X no clue Topoly V Jop temp

Almost all power goes to charging + Lischerging hodal caracitance C(V2) F Frequency Shitching shall VDD-() 50 have in 5 V If redo in WVPb = 3.3 V what speedup (change in F) (ald be specified & soundry want to keep power belget inchanged T don't get tub Oh P= ((V2) F Capationce same So basically 52 Ml = 3.32 F  $\frac{50}{3.32} = 2.29$ r assign Jalle

la possible 2-input combo logic gates Cost varies dramatically 6-210 karnargh maps -indicate min # of mosfets (need more practice with) - Static, full complerently - Vo4 = OV Voh = Vop - NFets pulldown - Compleventy - when one off other is on -Seller decompose into series + parallel connection mosfets - restore unitage

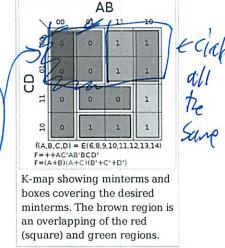

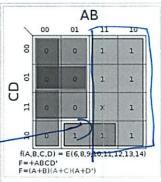

# Karnaugh map

From Wikipedia, the free encyclopedia

The Karnaugh map (K-map for short), Maurice Karnaugh's 1953 refinement of Edward Veitch's 1952 Veitch diagram, is a method to simplify Boolean algebra expressions. The Karnaugh map reduces the need for extensive calculations by taking advantage of humans' pattern-recognition capability, permitting the rapid identification and elimination of potential race conditions.

In a Karnaugh map the boolean variables are transferred (generally from a truth table) and ordered according to the principles of Gray code in which only one variable changes in between adjacent squares. Once the table is generated and the output possibilities are transcribed, the data is arranged into the largest possible groups containing  $2^n$  cells  $(n=0,1,2,3...)^{[1]}$  and the minterm is generated through the axiom laws of boolean algebra.

### **Contents**

- 1 Example

- 1.1 Truth table

- 1.2 Karnaugh map

- 1.3 Solution

- 1.4 Inverse

- 1.5 Don't cares

- 2 Race hazards

- 2.1 Elimination

- 2.2 2-variable map examples

- 3 See also

- 4 References

- 5 Further reading

- 6 External links

Race condition

-output is unexpectily/critically dependent

on sequence and liming of events

logic circits

multithreaded programs

# Example

Karnaugh maps are used to facilitate the simplification of Boolean algebra functions. The following is an unsimplified Boolean Algebra function with Boolean variables A, B, C, D, and their inverses. They can be represented in two different notations: